## Universidad Nacional de Ingeniería

Facultad de Ingeniera Ejectrica y Ejectrónica

# Diseño y Construcción de las Etapas de Entrada de un Transcodificador Digital NTSC - PAL/M

TESIS

PARA OPTAR EL TITULO PROFESIONAL DE INGENIERO ELECTRONICO

Manuel José Luis Ramírez Campos

Promoción 1982 · 1

lima - Perú 1985

# DISENO Y CONSTRUCCION DE LAS ETAPAS DE ENTRADA DE UN TRANSCODIFICADOR DIGITAL

NTSC-PAL/M

### INDICE

|                |                                                                   | Pag      |

|----------------|-------------------------------------------------------------------|----------|

| PROLOGO        |                                                                   | 1        |

| CAPITULO       | I : Aspectos Generales                                            | 5        |

| 1.1            | Introducción                                                      | 5        |

| 1.2            | El Sistema NTSC                                                   | 6        |

| 1.3            | Ventajas de usar procesamiento digital                            | 8        |

| 1.4            | Diagrama de bloques del sistema pro - puesto y puntos esenciales  | 10       |

| CAPITULO       | II: Etapa de Sincronismo                                          | 17       |

| 2.1            | Introducción                                                      | 17       |

| 2.2            | Concepción y diagrama de bloques de la etapa de sincronismo       | 18       |

| 2.2.1          | Características deseadas<br>Diagrama de bloques                   | 18<br>19 |

| 2.3            | Etapa de enganche con la subportadora (PLL)                       | 21       |

| 2.3.1 2.3.2    | Características deseadas<br>Circuito VCXO                         | 21<br>21 |

| 2.4            | Contador entre 910                                                | 26       |

| 2.4.1<br>2.4.2 | Características deseadas<br>Secuencia de cuenta e implementación  | 26<br>27 |

| 2.4.2.1        | Funcionamiento del contador                                       | 29       |

| 2.5            | Separador de Sincronismo                                          | 36       |

| 2.5.1<br>2.5.2 | Características deseadas<br>Etapas de regeneración de sincronismo | 36<br>37 |

| 2.5.2.1        | Separador de tierra analógica y digi-<br>tal para el sgnc         | 37       |

| 2.5.2.2        | Circuito de separación de los pulsos<br>H, 2H, 4H, V, 2V, 4V, K   | 38       |

| 2.6            | Separador de Burst                                                | 48       |

|                         |                                                                                                  | Pag.           |

|-------------------------|--------------------------------------------------------------------------------------------------|----------------|

| 2.6.1                   | Desacoplador de tierras analógica y<br>digital<br>Separación y amplificación del burst           | 48<br>49       |

| CAPITULO                | III: Etapa de Conversión Analógica/Di-<br>gital                                                  | 52             |

| 3.1                     | Introducción                                                                                     | 52             |

| 3.2                     | Esquema general y diagrama de bloques<br>de la etapa de conversión analógica /<br>digital        | 54             |

| 3.3                     | Circuito de entrada y regenerador de - sincronismo                                               | 57             |

| 3.3.1<br>3.3.2<br>3.3.3 | Circuito de entrada<br>Regenerador de sincronismo<br>Enclavador                                  | 57<br>57<br>59 |

| 3.4                     | Amplificador de video                                                                            | 63             |

| 3.4.1<br>3.4.2<br>3.4.3 | Especificaciones<br>Implementación<br>Resultados experimentales                                  | 63<br>63<br>66 |

| 3.5                     | Conversor Analógico/Digital                                                                      | 67             |

| 3.5.1<br>3.5.2<br>3.5.3 | Especificaciones<br>Implementación<br>Consideraciones sobre las tierras ana-<br>lógica y digital | 67<br>68<br>70 |

| CAPITIII.O              | <pre>IV: Filtro Pasabajo/Pasa alto</pre>                                                         | 72             |

| 4.1                     | Introducción                                                                                     | 72             |

| 4.2                     | Concepción y diagrama de bloques                                                                 | 73             |

| 4.2.1                   | Requerimientos mínimos<br>Diagrama de bloques                                                    | 73<br>75       |

| 4.3                     | Diseño del filtro                                                                                | <b>7</b> 9     |

| 4.3.1<br>4.3.2          | Elección de la configuración<br>Diseño                                                           | 79<br>81       |

| 4.4                     | Implementación del filtro                                                                        | 89             |

| CAPITULO                | V: Etapa Filtro Peine                                                                            | 91             |

| 5.1                     | Introducción                                                                                     | 91             |

| 5.2                     | Concepción y diagrama de bloques                                                                 | 95             |

|                   |                                                             | Pag.     |

|-------------------|-------------------------------------------------------------|----------|

| 5.2.1<br>5.2.2    | Cálculo del retardo del filtro peine<br>Diagrama de bloques | 95<br>99 |

| 5.3               | Implementación circuital                                    | 102      |

| CAPITULO          | VI: Implementación del Sistema Propuesto                    | 105      |

| 6.1               | Introducción                                                | 105      |

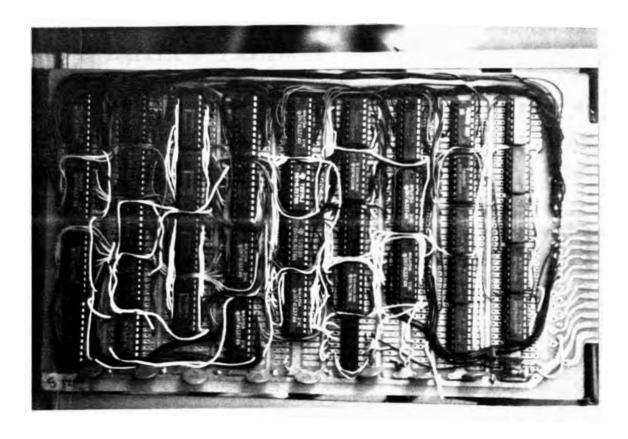

| 6.2               | Tarjetas Impresas                                           | 106      |

| 6.3               | El rack del sistema                                         | 109      |

| 6.4               | Etapa de sincronismo                                        | 113      |

| 6.5               | Etapa de conversión A/D                                     | 118      |

| 6.6               | Etapa filtro pasabajo/pasa alto                             | 120      |

| 6.7               | Etapa filtro peine                                          | 121      |

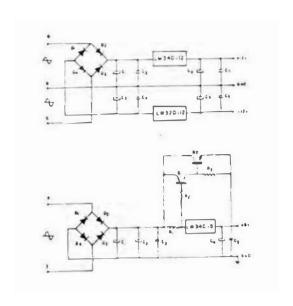

| 6.8               | Fuente de alimentación                                      | 128      |

| CONCLUSIO         | ONES                                                        | 130      |

| ANEXOS            |                                                             | 133      |

| I                 | Plano Circuital de la etapa de sincro-<br>nismo             | 134      |

| II                | Plano circuital de la etapa de conversión A/D               | 135      |

| III               | Plano del filtro pasa bajo/alto                             | 136      |

| IV                | Plano del filtro peine                                      | 137      |

| V                 | Tablas para los coeficientes del filtro pasa bajo           | 138      |

| VI                | Hoja de datos del conversor TDC 1007J                       | 146      |

| VII               | Hoja de datos del amplificador MC1550                       | 152      |

| VIII              | Hoja de datos de la memoria TBP 28L22                       | 153      |

| IX                | Hoja de datos de la memoria 2149H-3                         | 155      |

| BIBLIOGR <i>A</i> | AFIA                                                        | 157      |

### **PROLOGO**

El presente trabajo tiene como base el dise ño y construcción de un transcodificador digital NTSC - PAL/M desarrollado en el Laboratorio de Investigación del Instituto Nacional de Investigación y Capacitación en Telecomunicaciones (INICTEL). Este sistema se puede dividir claramente en tres partes:

Etapa de entrada (primera parte), que abarca desde la recepción de la señal de video hasta la separación digital de sus componentes Luminancia y Crominancia.

Etapa de salida (segunda parte), que comprende desde la -captación de la Luminancia y Crominancia separadas hasta la salida transcodificada de la señal de video a tratar.

Etapa de prueba (tercera parte), que abarca la generación de una señal de barras de color digital para la prueba de las diferentes etapas y del equipo en general.

El objetivo principal de este tema es mos trar en forma detallada el diseño y construcción de la

etapa de entrada (primera parte) de este transcodificador

digital NTSC-PAL/M para lo cual dicha etapa se ha subdivi

dido a su vez en 4 etapas:

- Conversión analógica/digital

- Filtro pasabajo/pasaalto

- Filtro peine

- Sincronismo (clock)

Las motivaciones para la elección de este tra bajo han sido: la importancia y trascendencia socio-econó mica que tiene en todos los países del mundo el dominio de estas técnicas así como los equipos y trabajos que de ella se derivan. En el caso particular del transcodificador NTSC-PAL/M permitirá que el Perú pueda exportar programas de televisión a los países que utilizan el sistema PAL/M.

Asimismo este equipo convenientemente ubicado en una de nuestras estaciones terrenas facilitaría la transmisión de eventos importantes en vivo y en directo a los países que usen el sistema PAL/M. Todo esto redunda - en ingreso de divisas y generación de trabajo así como una mejor difusión de nuestra cultura.

Cabe señalar que esta clase de herramientas - ya existen en el mercado mundial, pero los costos excesiva mente altos de su importación y el alto precio al cual se ofertan internacionalmente, hacen que las empresas naciona les vean pocas posibilidades de adquirirlos.

Frente a estas condiciones, el sistema que se presenta, se ha elaborado de modo que su implementación in volucre componentes y partes standard, es decir fáciles de conseguir en el mercado y por ende de bajo costo. De este

modo se presenta un prototipo competitivo en su género.

Se debe señalar que el diseño de estas fa ses si bien está orientado a la construcción de un trans codificador NTSC-PAL/M, es válido también para otras aplicaciones incluyendo a las del campo del radar tan importante para efectos de seguridad de la nación.

Para un mejor entendimiento de lo que se pretende exponer, se ha dividido este trabajo en cinco Ca pítulos de los cuales el Capítulo I hará una descripción más precisa de los alcances y limitaciones del proyecto y esbozará consecuentemente los diagramas de bloques. En los Capítulos II, III, IV y V se describirán respectivamente cada una de las cuatro etapas que componen nuestro sistema, se realizan los diagramas de bloques, los dise nos de los circuitos involucrados y se presenta el circuito final.

Este trabajo se desarrolló en el Laborato rio de Investigación de INICTEL, bajo la asesoría del In geniero alemán Hans Peter Maly, experto en el área de Pro cesamiento Digital de Señales de Video, a quien agradezco haberme dado la oportunidad de trabajar con él y adquirir la experiencia para el desarrollo de este tema. Además, mi reconocimiento a mis amigos y compañeros de trabajo del Laboratorio de Investigación de INICTEL en especial al Ing. Miguel Cabrera, Ing. Jorge Barriga, Ing. Enrique Cal derón, así como al Ing. Pedro Heredia Martinetti, mi ase

sor, quienes en todo momento y de una u otra forma me brindaron ayuda valiosa y alentaron en la ejecución del presente tema.

Asimismo mi agradecimiento al Ing. Miguel Segami quien hizo posible la presentación de las vistas fotográficas y a la Srta. Edda Salazar quien realizó el tipeado colaborando significativamente a la mejor presentación de este trabajo.

### CAPITULO I

### ASPECTOS GENERALES

### 1.1 Introducción

En el presente capítulo se proporcionarán - las ideas fundamentales que servirán como base para la compresión del sistema propuesto "ETAPA DE ENTRA DA DE UN TRANSCODIFICADOR DIGITAL NTSC-PAL/M".

En vista de que este diseño es aplicado al sistema NTSC, se hace un estudio de las características de este sistema, además se explican los alcan ces y limitaciones del presente diseño y se da un es bozo del diagrama de bloques del sistema propuesto.

### 1.2 El sistema NTSC

El sistema NTSC pertenece a la norma M, es decir: 525 líneas/60 campos. En cuanto al sistema propiamente dicho el principio de la codificación del color se basa en la modulación de amplitud y fase (sa turación y matriz de color) de una sub-portadora, es decir esta es una modulación en cuadratura con la portadora suprimida. La señal así codificada es super - puesta con la señal blanco y negro, (la luminancia).

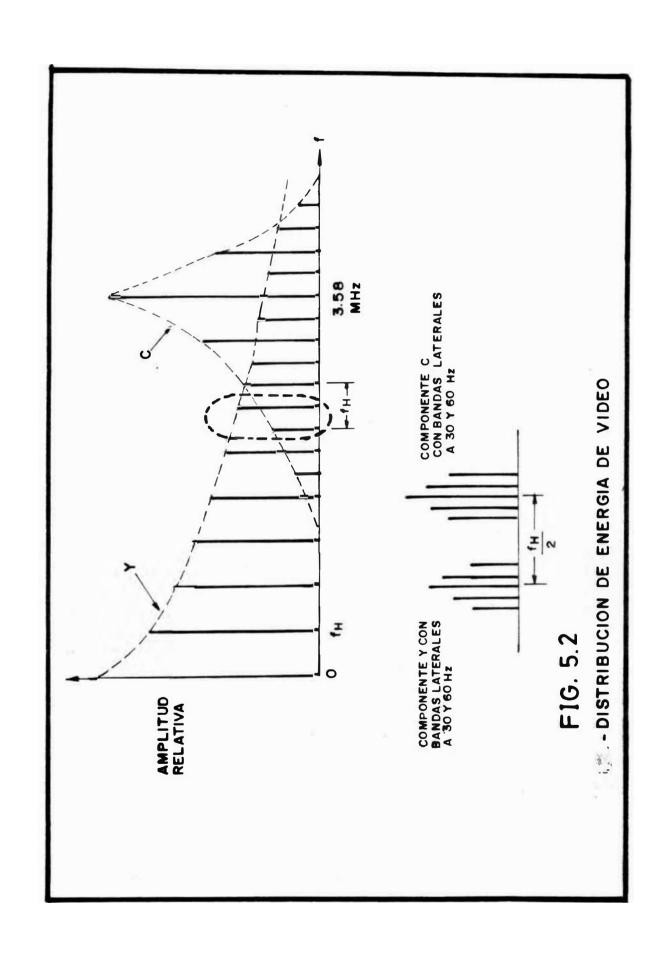

La superposición de la luminancia y la crominancia, se realiza aprovechando el hecho que el espectro de energía de frecuencia tiene la característica de un espectro de líneas; en este caso la luminancia y la crominancia quedarán con las líneas de frecuencia entrelazadas.

En el sistema NTSC la frecuencia de la subportadora tiene una relación fija con respecto a la frecuencia horizontal:

fsp= (2n + 1) fh/2

fh = frecuencia horizontal

n = 227

Esto significa que existen 227.5 ciclos de la sub-portadora en cada línea horizontal.

En el sistema NTSC se define el término

"offset de media línea", debido al medio ciclo que

finaliza en la línea horizontal. Esto hace que en

dos líneas consecutivas, la fase de la subportadora esté desplazada 180°

La frecuencia de la subportadora en NTSC es de fsp = 3.579545 MHz, ubicandose de esta manera - entre dos líneas del espectro de frecuencias de la luminancia (exactamente en la mitad) y separada a ca da lado por media frecuencia horizontal.

### 1.3 Ventajas de usar procesamiento digital

Antes de seguir con la descripción más deta llada de las etapas de procesamiento, se debería discutir el porque proyectar un procesamiento digital y cuáles son sus ventajas con respecto a las técnicas analógicas.

En general la técnica digital ofrece ventajas inherentes a los circuitos digitales, tales como

insensibilidad con respecto a influencias ambientales;

evita la necesidad de puntos de ajuste; brinda posibi

lidades adicionales de procesamiento de señales.

Como ejemplo se podría decir que en este caso no se necesitarán circuitos analógicos complicados con filtros y demoduladores para separar la luminan - cia de la crominancia, y que posiblemente requeriría muchos puntos de ajuste. En vez de esto se utilizará un filtro peine que necesita un elemento de retardo - de 64 us y un ancho de banda de 4.2 MHz. En la forma digital este retardo se realiza por medio de memorias RAM sin problemas de ancho de banda y sin ajustes ya que el retardo viene asegurado exactamente por una - línea de reloj.

Además, cabe destacar que este proyecto se ha escogido por su actualidad y que por su realiza - ción toca muchas áreas del procesamiento de señales-

en general, es decir no solamente relacionadas a video.

# 1.4 <u>Diagrama de bloques del sistema propuesto y puntos</u> esenciales

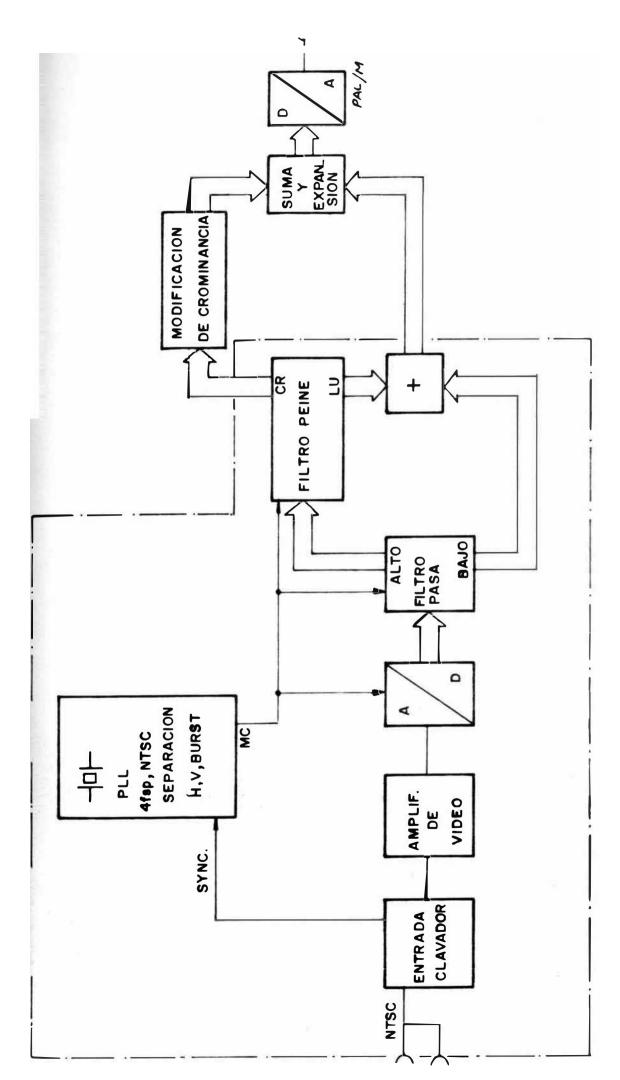

En la figura 1.1 se muestra el diagrama de bloques general del sistema propuesto.

Debido al desarrollo avanzado de los circui tos integrados no tenemos que preocuparnos de los circuitos de conversión analógico/digital y digital/analógico.

El principio adecuado para la conversión se llama "conversión flash" que consiste en convertir - una señal de video con una velocidad de 15 millones - de muestras por segundo, aproximadamente y codificada con 8 bits por palabra.

En el contexto de las conversiones A/D y D/A cabe justificar la frecuencia de muestreo. Teori camente se necesitaría una frecuencia para tomar mues tras, más alta que el doble de la frecuencia máxima - de la señal analógica; en el caso del sistema NTSC sería más de 9 MHz. Sin embargo, por razones de faci lidad en el procesamiento digital se escoge un múltiplo de la frecuencia de la subportadora.

En el sistema propuesto la señal NTSC de en trada es muestreada con el cuádruplo de la subportado ra, es decir 14.318180 MHz.

De esta forma la conversión A/D hace que se tomen muestras en 0, 90, 180 y 270 grados con respecto a la fase de la subportadora en reposo. En el pla no de la modulación de crominancia esto significa que las muestras son tomadas en los ejes 'U' y 'V' . Si prescindimos en este punto de la luminancia, la serie de muestras es una serie de valores de las señales de diferencia de color: 'U' 'V' "-U" y "-V".

Para separar los componentes de la señal de video, luminancia y crominancia, se usa el filtro peine, el cual nos asegura una degradación mínima de la calidad de los componentes.

Como se mencionó anteriormente, el espectro de frecuencia de la señal NTSC compuesta es un espectro de líneas. Tanto las líneas del espectro de la luminancia como las de la crominancia están separadas por una distancia equivalente a la frecuencia horizon tal. Pero las líneas del espectro de luminancia y las líneas del espectro de crominancia están entrelazadas con un offset equivalente a media frecuencia horizontal. Para separar la crominancia del espectro de la señal compuesta, se necesita un filtro cuya respuesta sea cero en los lugares donde están las líneas de la luminancia y sea uno para los lugares donde están las líneas de la crominancia.

Un filtro que tenga las cualidades anteriores -

deberá tener una curva de respuesta cuya forma es la del valor absoluto de la función seno y cuyo período sea el doble de la frecuencia horizontal. El filtro en mención se denomina filtro peine y consiste en un elemento de retardo y un punto de sustracción de la señal actual retardada. La respuesta inversa de este filtro es apropiada al realizar la separación de las líneas de luminancia, en cuyo caso se necesitará además un punto de suma de la señal actual y la señal retardada.

En el filtro peine se aprovecha el hecho de que dos líneas horizontales de video consecutivas tie nen casi la misma información y además que por el efecto del offset de media línea las fases de la crominancia en dos líneas consecutivas son opuestas. De este modo en el punto de sustracción se elimina la lu minancia y se dobla la crominancia. Por el contrario en la salida del sumador se elimina la crominancia y se dobla la luminancia.

Evidentemente el filtro peine afecta a la señal de video ya que causa la interpolación de la in formación de líneas consecutivas. Para no perder re solución vertical hay que limitar el proceso del filtro peine, para el rango donde se encuentran entrelazados los espectros de luminancia y crominancia (2.4 MHz - 4.2 MHz). Por medio de un filtro pasa bajo, se realiza entonces un desvío para las frecuen -

cias bajas (solo luminancia) y se aplica el proceso de filtro peine solo para el rango de entrelazamien - to.

Para la línea de retardo se usan memorias - RAM cuyo tiempo de acceso sea menor que 70 ns. Dichas memorias deberán almacenar 910 muestras, equivalentes a una línea horizontal. Por lo tanto necesitamos dos memorias de 1k x 8 bits cambiando el modo de operación en cada línea respectivamente, es decir que mientras una memoria esta guardando la información de la línea actual, de la otra memoria se lee la información de la línea anterior. Contadores controlados generan las direcciones para leer y escribir para efectuar un retardo de 910 ciclos de reloj (una línea).

El filtro pasa bajo se realizará con un filto transversal no recurrente, que tendrá una estructura de cadena formada con registros, donde cada uno retarda la señal de un ciclo de reloj (1/4 fsp = 70 ms). Las tomas, es decir los puntos entre registro y registro son multiplicadas con coeficientes simétricos y están llegando a un punto donde se suman. Este fil tro tiene la ventaja de que el retardo de grupo estabsolutamente constante y los cálculos son simples.

En el diagrama de la figura 1 se observan - las etapas en que está dividio el sistema propuesto La etapa de conversión analógica/digital es aquella

donde se digitaliza la señal de video de entrada; ésta etapa contiene al conversor A/D propiamente dicho y también al circuito enclavador que realiza 2 funcio nes muy importantes : fija la señal de video a niveles que estén dentro del rango de entrada del conversor -A/D y además realiza la separación del sincronismo de la señal de video. Luego viene la etapa del Filtro Pasa bajo/alto, el cual entrega a la siguiente etapa la parte de la señal de video en la que la luminancia y la crominancia se encuentran entrelazadas, es decir, desde 2.4 MHz hasta 4.2 MHz aproximadamente. quiente etapa es el filtro peine el cual realiza separación efectiva de la luminancia y la El control y temporización de todas estas eta pas lo proporciona la etapa de reloj en la cual PLL hace el enganche del reloj del equipo con el Burst de la señal de video.

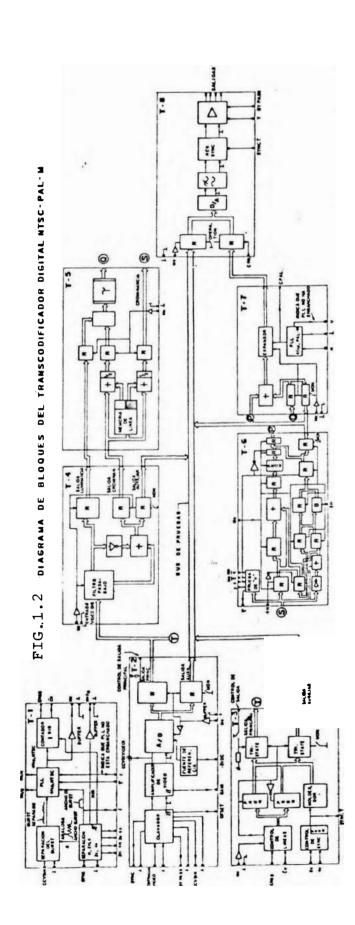

En la figura 1.2 se muestra un diagrama en el que se puede ver todas las tarjetas del transcodificador y su interrelación a nivel de bloques. En es te trabajo nos referiremos a las signadas como T-1, -T-2, T-4 y T-5.

DIAGRAMA DE BLOQUES GENERAL DEL SISTEMA PROPUESTO F16.11

### CAPITULO II

### ETAPA DE SINCRONISMO

### Introducción

Este capítulo tratará todo lo referente a - la concepción, diseño y construcción de la circuite - ría necesaria para obtener las señales adecuadas de modo que se pueda realizar un procesamiento sincronizado de la señal de video.

Esta tarjeta cumple un papel muy importante en el buen funcionamiento del equipo. Se ha concebido esta etapa de manera que el conjunto de señales generadas permita buena sincronización con la señal de entrada en las diversas formas de procesamiento de la misma.

Para una mejor comprensión se ha dividido el capítulo de modo que se puedan explicar, primero la idea global del requerimiento del sistema en esta etapa, y luego se explican aisladamente cada etapa - de manera que al final del capítulo éstas puedan ser integradas en un circuito final.

# 2.2 <u>Concepción y diagrama de bloques de la etapa de</u> sincronismo

Esta etapa se ha estructurado de tal manera que proporcione las señales necesarias para sincronizar las diferentes partes del procesamiento digital de la señal de video NTSC.

### 2.2.1 Características deseadas

Se utiliza como base la propia señal de video NTSC de entrada y a partir de esta se lo

grará lo siguiente:

- 1.- Sincronizar la frecuencia de tomar mues tras (cuádruplo de la frecuencia de la sub portadora) con el burst de la señal de vi deo (cuya frecuencia es igual a la fre cuencia de la subportadora y es la refe rencia en fase para decodificar toda la croma).

- 2.- Regenerar el sincronismo horizontal, el sincronismo vertical, una señal que nos permita diferenciar las lineas pares de las lineas impares; también es necesario diferenciar los campos que hemos denomina do campo I y campo II.

- 3.- Es necesario la realización de un divisor

de frecuencia entre 910 de tal modo que al entrar como reloj la frencuencia de tra bajo (14.318180 MHz) se catenga la frecuen cia horizontal como salida de este conta dor. La señal que se consiga a partir de este contador debe estar sincronizada con el sincronismo horizontal de la señal de entrada, lo que permitirá que las salidas de este contador tengan una relación fija con cada muestra de la señal de video en una línea horizontal. Esto da lugar a una realización más simplificada de las etapas de prueba de video cuya salida esté sincro nizada con la señal de entrada.

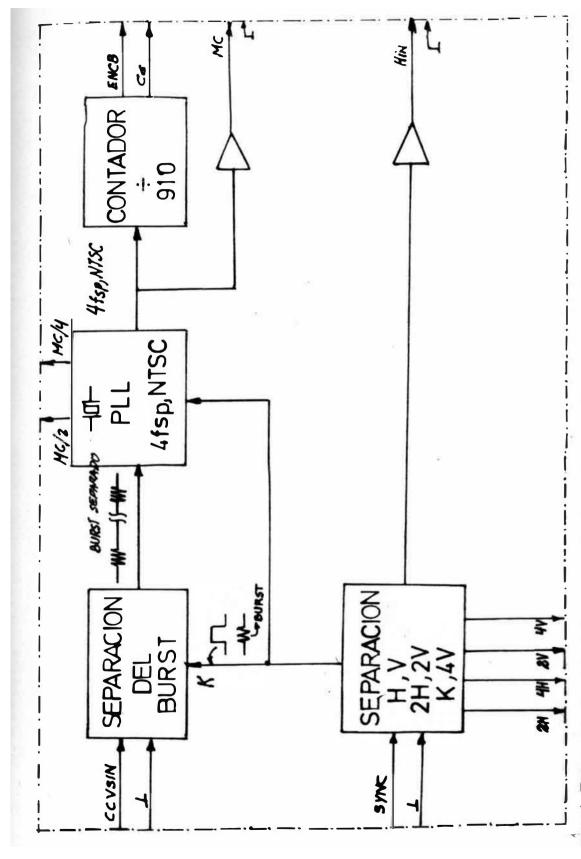

### 2.2.2 Diagrama de bloques

Las condiciones anteriores nos conducen - al siguiente diagrama de bloques (Fig.2.1).

En el esquema presentado se ha considerado incluir circuitos que realizan el desacopla miento de las tierras analógica y digital lo cual nos facilita sobremanera el procesamiento de las señales analógicas ya que de lo contra - rio un ruido de la frecuencia del VCO se intro- ducirá por la tierra analógica afectando la ca- lidad de la señal. Este circuito deberá pre sentar alta impedancia de entrada, tomándose -

FIG211-Diagrama de bloques de la etapa de sincronismo

luego la señal desde su colector con respecto a la tierra digital.

### 2.3 Etapa de enganche con la subportadora (PLL)

### 2.3.1 Características deseadas:

Como anteriormente se explicó, la velocidad de muestreo de la señal analógica será igual al cuádruplo de la frecuencia de la subportadora de color de la señal NTSC. Es decir

siendo  $f_{SC} = 3.579545 \text{ MHz} + 10 \text{Hz}$  la frecuencia de la subportadora de video NTSC.

$$f_{\text{muestreo}} = 14.31818 \text{ MHz} + 40 \text{Hz}$$

El VCO deberá trabajar a ésta frecuencia y su rango de variación deberá estar comprendido entre 14'318,180 + 40Hz y 14'318,180 - 40Hz de tal manera que el circuito en mención deberá poseer un alto factor de calidad que nos permita mantenernos dentro del rango señalado.

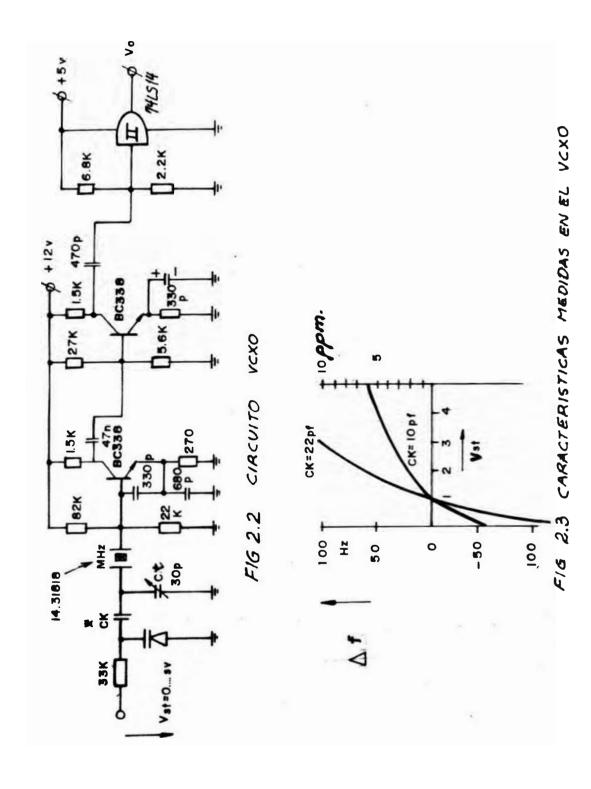

### 2.3.2 Circuito VCXO

Después de haber ensayado diferentes tipos de osciladores encontramos la configuración

mostrada en la figura (2.2) que no posee ele mentos inductivos y cuya implementación es sen

cilla.

El presente se destaca por emplear un cir cuito resonante serie.

El VCXO presentado funciona de la siguie $\underline{\mathbf{n}}$  te manera:

El voltaje aplicado en la entrada del cir cuito causa que el varicap presente una capac $\underline{i}$  dad dada que acoplada mediante  $C_K$  y conjunta - mente con  $C_+$  forman una capacidad equivalente.

Esta capacidad equivalente y el circuito equivalente del cristal forman el circuito re sonante serie. En la frecuencia resonante la impedancia de este circuito es mínima (ya que funciona en resonancia serie) y fluye por él la máxima corriente. En el paso de la corriente te también están incluidos  $C_6$  y  $C_7$  en cuanto al circuito resonante serie, por lo que en la frecuencia de resonancia aparece una aprecia ble caída de tensión entre los bornes de estos condensadores. La caída de tensión que aparece entre los terminales de  $C_6$  es amplificada por  $Q_1$  mientras que la salida del amplificador aparece sobre  $C_7$  como potencia de exitación para mantener la oscilación en el circuito.

El nivel de señal obrenido en el colector de  $Q_1$  es muy bajo siendo por ello necesario un amplificador formado por  $R_{28}$ ,  $R_{30}$ ,  $R_{31}$  y  $Q_2$  que reciben la señal por acoplamiento capacitivo por medio de  $C_{Q}$ .  $C_{Q}$  ha sido colocado para aumentar la ganancia en alterna. Ya que nosotros necesitamos trabajar con niveles TTL necesitamos que ésta oscilación sinusoidal sea cuadra da y oscile entre dichos voltajes. Esto se logra con una red de acoplamiento formada por  $C_{10}$ ,  $R_{32}$  y  $R_{33}$  y un Schmitt Trigger 1/6 74LS14, de ésta forma la señal simusoidal amplificada es convertida a niveles TTL, obteniéndose así un VCXO con niveles de salida tales que puedan ser usados por los circuitos de la serie y otros.

Durante la implementación practicada de dicho VCXO pudimos observar que aplicando una tensión continua en la entrada del mismo podia mos variar las características de la red contro ladora de la frecuencia de tal manera que se - obtenían variaciones en partes por millón al rededor de la frecuencia central es decir, la frecuencia del cristal 14.318180.

Asimismo la variación del condensador de acoplamiento  $\mathbf{C}_{K}$  provoca una modificación en la linealidad de la variación de la frecuencia

con la tensión aplicada. La variación de  $C_{\mathsf{t}}$  provoca un ligero corrimiento de la frecuencia central de oscilación.

Estas características medidas se muestran en la Figura (2.3).

### Contador entre 910

### 2.4.1 Características deseadas:

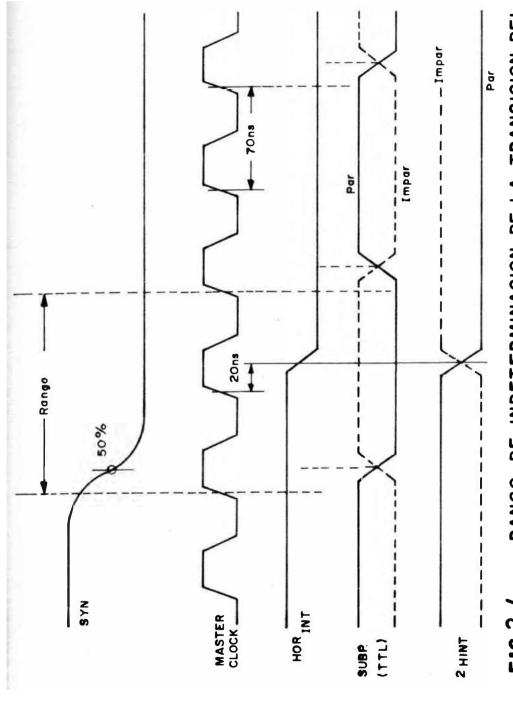

Para el procesador de video que se propone todo el procesamiento depende del buen acopla miento de la frecuencia de muestreo reloj - principal ó master clock ) y la subportadora , ya que hay tomar muestras en los ejes U y V. Además muchas etapas del procesamiento de la señal de video necesitan tener una relación respecto al sincronismo horizontal cuyo punto de referencia es su transición negativa (50% de su tiempo de caída).

Por medio de un contador que cuenta 910 ciclos del reloj principal, se tiene que gene rar una frecuencia horizontal que tiene una relación definida respecto de la fase la subportadora para uso interno, además hay que lograr que ésta frecuencia horizontal tenga una relación con el sincronismo de entrada de tal forma que la divergencia sea menor que clo del reloj principal (master clock) 70 De ésta manera produciremos una fre cuencia horizontal interna que va a ser la ferencia para todas las etapas. Véase la Figu ra (2.4) para mayor aclaración.

Además posteriormente hay que reconocer - laslíneas pares e impares por medio de la fase de la subportadora con respecto al impulso de la frecuencia horizontal interna.

En la figura se ve que el rango de inde terminación de la transición del SYNC es un me dio ciclo de la subportadora. Si no se consi dera este rango, ésta línea horizontal será redefinida como impar en lugar de par ó vice versa. Es evidente que tenemos que realizar - una especie de histéresis temporal para que el jitter del SYNC no pueda causar un cambio del orden a cada rato si se encuentra al límite del rango.

Como se ha dicho entonces, la frecuencia horizontal interna (generada por el contador) va a ser la referencia para todas las etapas que necesiten impulsos que dependan de la línea horizontal.

### 2.4.2 Secuencia de cuenta e implementación:

Todo procesador de video incluye otras fa cilidades dentro de la estructura de su sistema. En nuestro caso pretendemos incluir una tarjeta generadora de una señal de prueba de barras de televisión a colores, para mayor fa

RANGO DE INDETERMINACION DE LA TRANSICION DEL SYNC CON RESPECTO A LA SUBPORTADORA F16.2.4

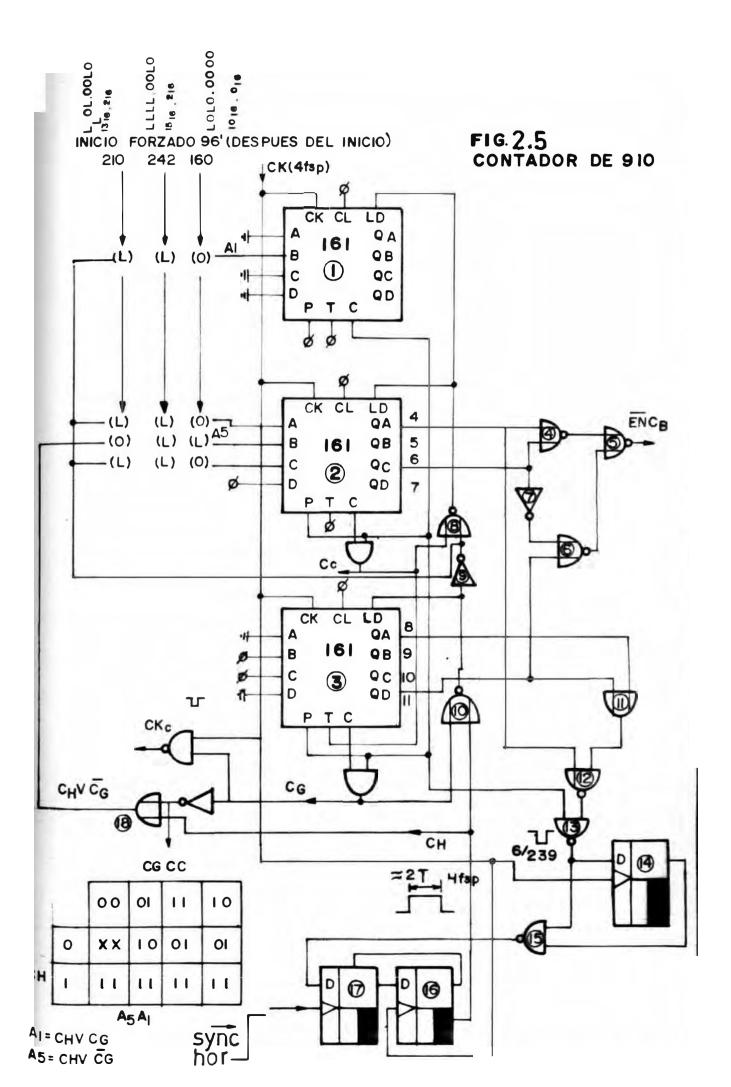

cilidad en construcción del control para las - memorias de la misma aprovecharemos la oportunidad que vamos a realizar un contador de 910 que genere un pulso H<sub>INT</sub> que esté sincronizado con el SYNC de entrada. Cabe aclarar que si no hiciéramos este artificio en la secuencia de cuentas, la realización del contador sería más directa y más sencilla. En la figura 2.5 podemos apreciar la realización del contador entre 910 antes mencionado. Se han utilizado 3 contadores binarios 74LS161 dispuestos en cascada y conectados siguiendo la técnica Ca rry Look Ahead.

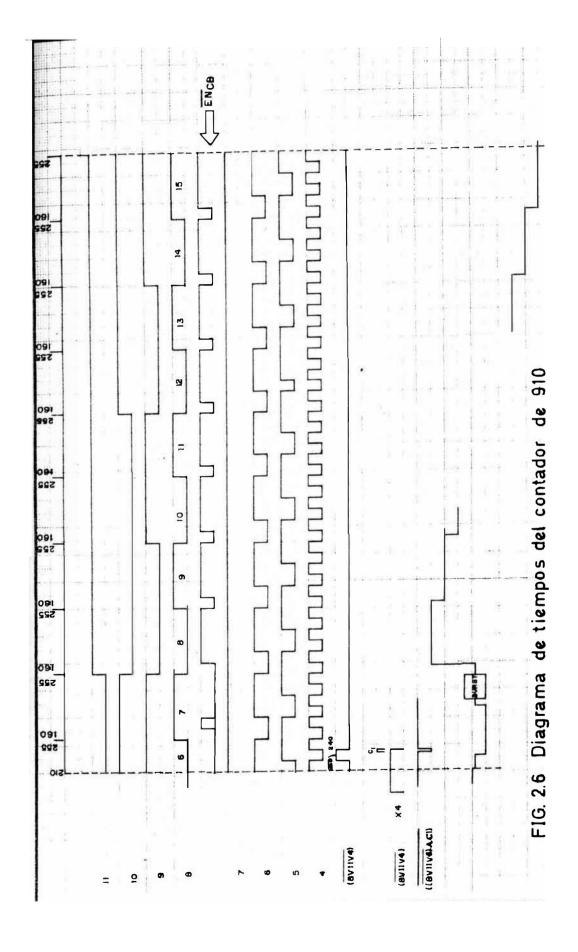

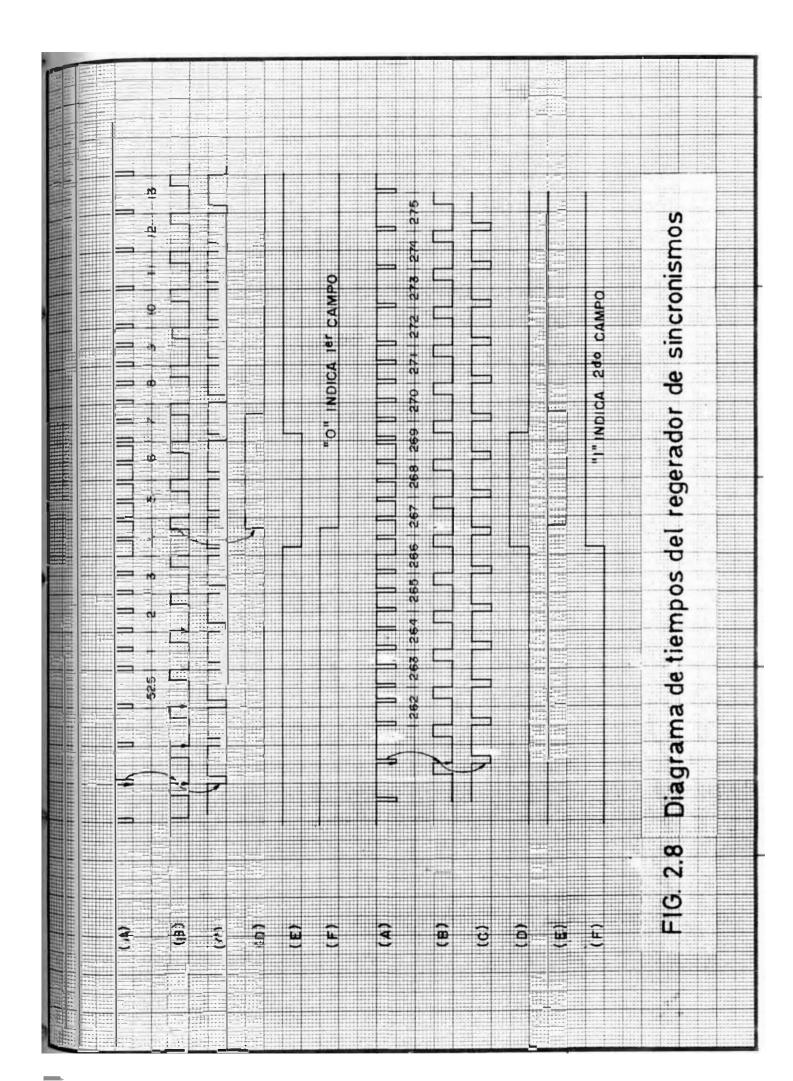

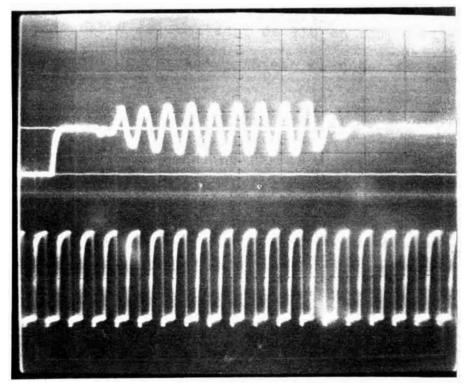

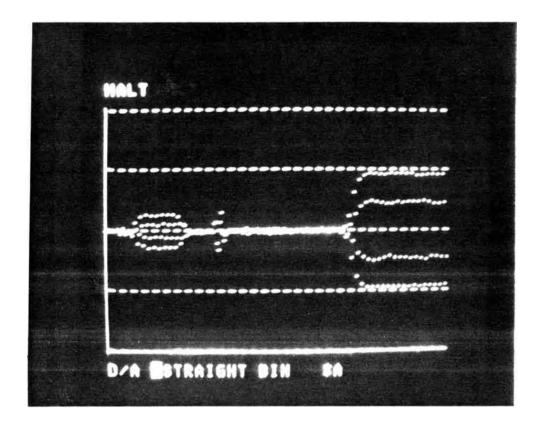

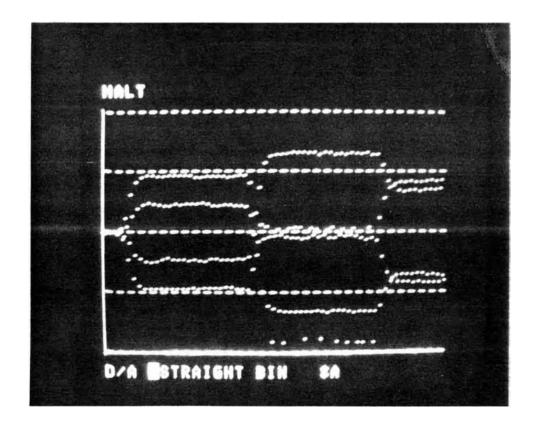

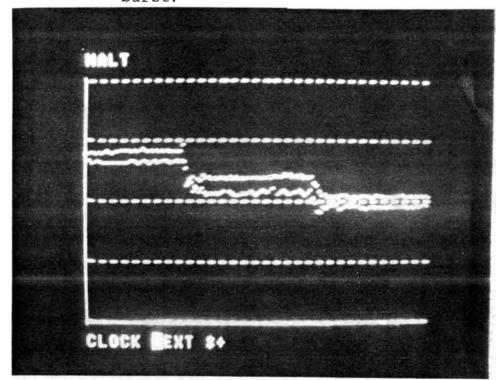

En la figura 2.6 podemos apreciar el dia grama de tiempos que produce este contador.

### 2.4.2.1 Funcionamiento del contador:

Este diseño fue realizado de tal manera de dividir entre 910 la frecuencia del master clock y obtener de este modo la frecuencia horizontal así como también para obtener señales que nos permitan efectuar el control para los circuitos del generador de Barras ó Tarjeta Test. Especialmente por ésta última razón, este contador

debe estar sincronizado con la frecuen cia horizontal del SYNC de entrada.

Para explicar el funcionamiento de este contador supongamos que el SYNC de entrada está, digamos, enganchado con la frecuencia horizontal que genera este contador (de este mo do al circuito que fuerza el enganche lo estaremos deshabilitando por el mo mento). Estando el contador en estas condiciones normales de trabajo, hace 910 cuentas del master clock o reloj principal después de lo cual entrega un "CARRY" en sus contadores parcia les; éstos pulsos decodificados cuadamente, ordenan a los contadores cargarse con el binario 210, tal como se ve en el diagrama del circuito У en el diagrama de tiempo. FIG. 2.5 FIG. 2.6. Acto seguido los contado res 1 y 2 contando hasta 255 comple tan un total de 46 estados, estos tregan un Carry que hará avanzar la cuenta del contador 3 desde 6 hasta 7 como puede apreciarse en el diagrama FIG. 2.5. Los "CARRY" de los conta dores 1,2 y 3 se decodifican adecua

damente para interpretar el término de esta primera cuenta de 46 estados

como cargar los contadores 1 y 2 con

el número 160 en binario. Los contadores 1 y 2 , luego seguirán contando hasta 255, computando un total de

96 estados, al final de los cuales

los pulsos de Carry de los contadores

1,2 y 3 decodificados adecuadamente ordenarán una nueva carga con el núme

ro 160 para los contadores 1 y 2 y

además el contador 3 avanza una cuen

ta y se pone ahora en 8.

Esta acción de los contadores 1 y 2 se repite hasta que el contador 3 llegué a su cuenta 15 completando un total de 10 cuentas.

Si hacemos una operación de veri ficación veremos que

$1 \times 46 + 9 \times 96 = 910$  cuentas

con esta forma caprichosa de contar - hemos realizado las 910 cuentas y además hemos logrado formar el diagrama de tiempos de la FIG. 2.6

Mediante los circuitos digitales

11,12,13,14,15,16 y 17 se realiza la sincronización del  $H_{\mathrm{INT}}$  generado y el SYNC. Esto se hace colocando una ven tana que tiene una duración de aproximadamente 2 períodos del master clock

140 ns) con esta ventana y el SYNC se hace una prueba con los flip flops 16 y 17. Si el flanco de subida del SYNC cae dentro de esta ventana, el contador seguirá su secuencia normal (la explicada anteriormente) en cambio si se encuentra fuera de esta ventana el circuito ordenará carga del contador con el número que para el generador de barras equi vale a la ubicación de la transición del sincronismo horizontal como prueba de la ventana se realiza cada vez que ocurre la transición del cronismo de entrada se asegura que en la siguiente linea, el SYNC de entrada estará relacionado con el  $H_{\text{INT}}$  ge nerado por el contador y estará en fa se con el sincronismo del generador de barras.

En la Figura 2.5 se puede apre - ciar como se decodifican los pulsos

11,12,13,14,15,16 y 17 se realiza la sincronización del  $H_{\mathrm{INT}}$  generado y el SYNC. Esto se hace colocando una ven tana que tiene una duración de aproximadamente 2 períodos del master clock

140 ns) con esta ventana У el SYNC se hace una prueba con los flops 16 y 17. Si el flanco de subida del SYNC cae dentro de esta ventana, el contador seguirá su secuencia normal (la explicada anteriormente) en cambio si se encuentra fuera de esta ventana el circuito ordenará carga del contador con el número que para el generador de barras equi vale a la ubicación de la transición del sincronismo horizontal como prueba de la ventana se realiza cada vez que ocurre la transición del cronismo de entrada se asegura que en la siguiente linea, el SYNC de entrada estará relacionado con el  $H_{\text{TNT}}$   $g\underline{e}$ nerado por el contador y estará en fa se con el sincronismo del generador de barras.

En la Figura 2.5 se puede apre - ciar como se decodifican los pulsos

${\rm C_{_{C}}}$  (Carry del segundo contador),  ${\rm C_{_{G}}}$  (Carry del tercer contador) y  ${\rm C_{_{H}}}$  (pul so resultante de la prueba de sincronismo) para cargar los contadores con los números apropiados.

Con el contador sincronizado se puede obtener una señal útil para el generador de barras. Esta señal es la ENCB que se obtiene docodificando las salidas de los contadores mediante el circuito lógico formado por 4, 5,6 y 7. Esta señal servirá como se verá posteriormente en la explicación de la Tarjeta Test, para ahorrar gran capacidad de memoria.

#### 2.5 Separador de sincronismo

#### 2.5.1 Características deseadas:

El separador de sincronismo es una etapa destinada a crear todos los pulsos nece sarios a partir de la señal SYNC que viene de la tarjeta A/D.

Es evidente que antes de realizar - algún proceso sobre esta señal SYNC es necesa rio realizar una separación entre la tierra - análoga y la tierra digital en el punto de en trega de este señal con la intención de que - las señales digitales no se introduzcan sobre las señales análogas a través de la unín de - éstas tierras.

Como se ha dicho la frecuencia hori zontal interna (generada por el contador), va a ser la referencia para todas las etapas que necesitan impulsos que dependan de la línea - horizontal.

Pero además hay que reconocer las líneas pares e impares por medio de la fase

de la subportadora con respecto al impulso de

la frecuencia horizontal interna.

En el párrafo anterior se habló res pecto a las líneas pares y las líneas impares

con respecto a la subportadora. La cantidad - de líneas por imagen (525) es un número impar, por eso en ese sentido las líneas pares de una imagen vienen a estar ubicadas en los tiem pos relativos a las líneas impares de la otra imagen (otras 525 líneas) y viceversa dependien do de esta relación podemos definir dos image nes diferentes.

Los dos campos de una imagen se  $pu\underline{e}$  den diferenciar por medio de la parte vertical del impulso de SYNC con respecto a su fase con la frecuencia horizontal.

### 2.5.2 Etapas de regeneración de sincronismo

## 2.5.2.1 <u>Separador de tierra analógica y digi</u>tal para el SYNC :

Como antes se dijo se hace necesario que existan elementos que desa coplen las tierras analógicas y digitales para que las señales analógicas no se vean perjudicadas por las seña les digitales.

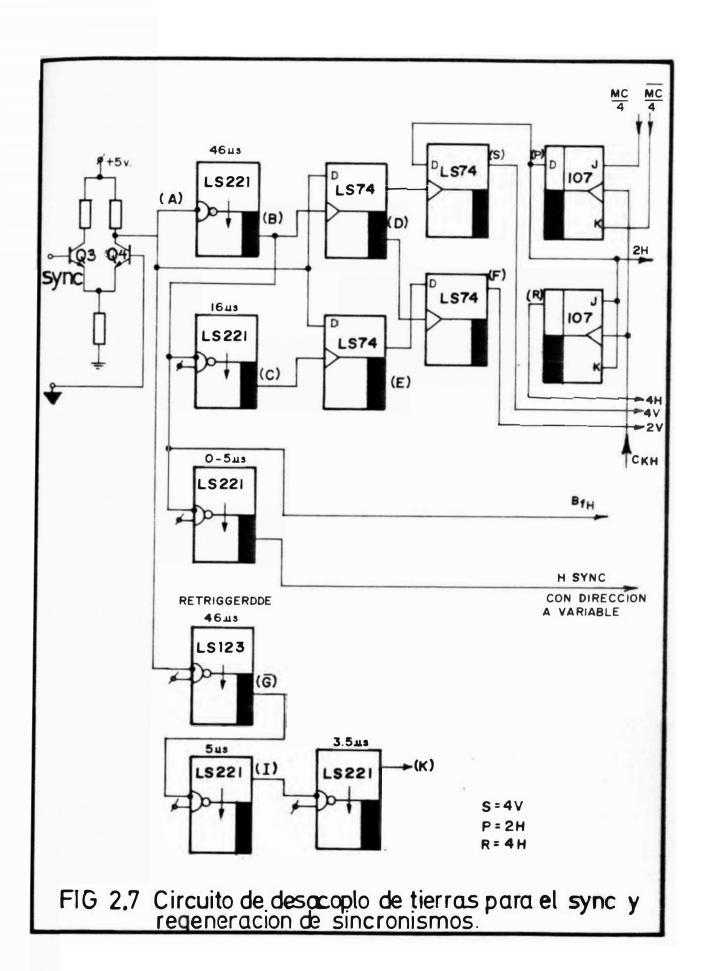

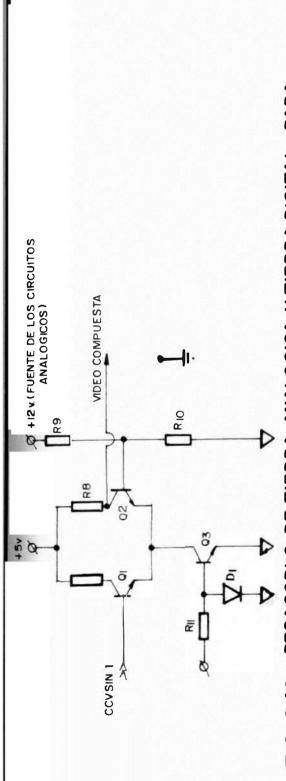

Hemos escogido el siguiente cir cuito FIG. 2.7 .

Como se puede observar la inten ción es tratar de crear el mayor desa coplo posible entre la señal, con tierra analógica aplicada a las bases y la señal con tierra digital. Para lograrlo utilizamos el arreglo de un CA3051, que se presenta bastante propicio para ésta aplicación ya que presenta alta impedancia de entrada aislando en forma efectiva la señal de entrada de la de salida aunque siempre existe cierta influencia en este mis mo circuito entre ambas señales.

La señal ingresa al circuito emu lando un comportamiento en modo diren cial puro (aunque ciertamente no lo es) de modo que por una base ingresa la señal SYNC que viene de la tarjeta A/D y por la otra base llega su refe rencia que es la tierra analógica. La señal de salida es tomada del colec tor de  $Q_4$  con respecto a la tierra di gital. Figura 2.7 .

# 2.5.2.2 <u>Circuito de separación de los pulsos</u> H,2H,4H,V,2V,4V,K:

Esta circuitería es necesario

verla en su conjunto y en la figura - 2.7 se puede apreciar el diagrama com pleto de los circuitos que realizan - esta tarea.

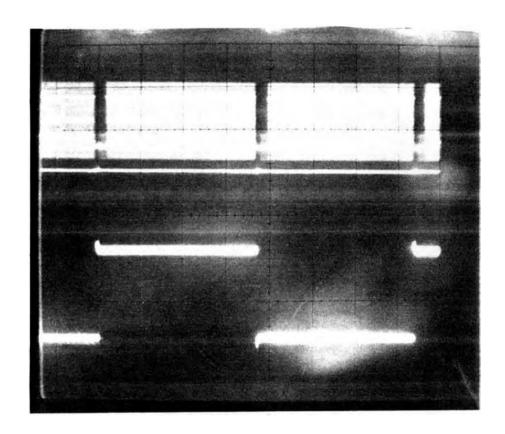

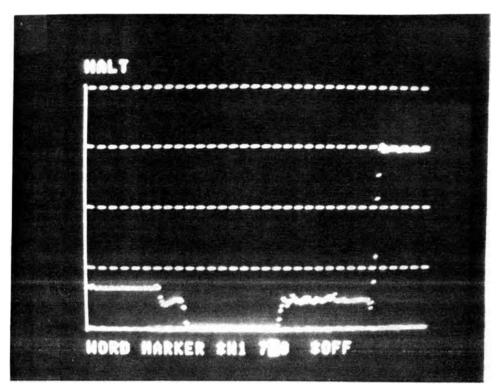

Como se ve la señal tomada del colector del separador de tierras es el SYNC. En la figura 2.8 la señal (A) es la que muestra la forma de onda del SYNC. En esta figura se ha representado la misma señal en sus dos formas características ya que el SYNC varía en su forma en 2 campos consecu tivos. Siempre que nos remitamos a la figura 2.8 veremos las 2 porciones, superior e inferior de la misma para efectuar las comparaciones del caso.

La señal (A) que es el SYNC se usará como base para la regeneración de la mayor parte de los pulsos.

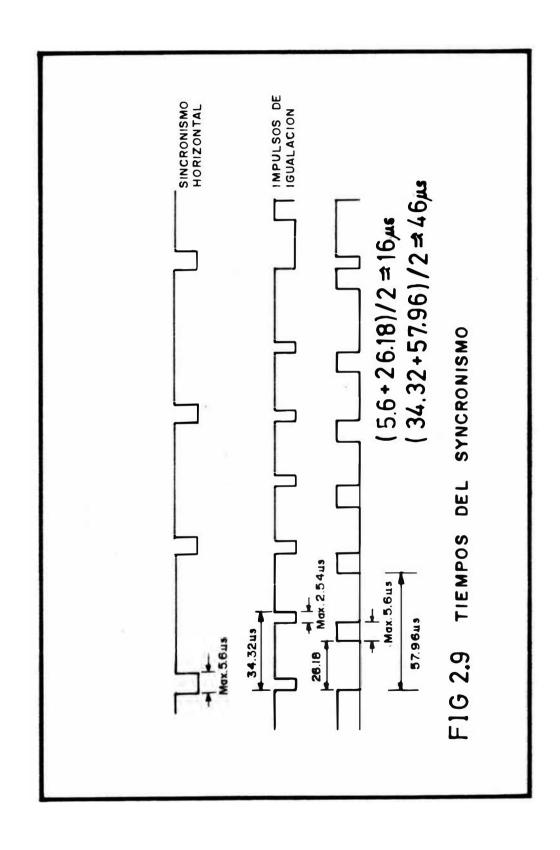

Las señales (B) y (C) son señales que tienen la frecuencia horizontal y que servirán como herramientas para conjuntamente con (A) obtener las se ñales características (D) y (E) que tienen la frecuencia vertical. La obtención de los monoestables de 46us y

16us se explica claramente en la figura 2.9. Como se ve en la figura 2.7 aplicando (B) como clock de un FLIP FLOP tipo D y (A) como entrada D se obtiene la señal (D) de frecuencia del sincronismo vertical pero que en cada campo tiene una ubicación característica como se aprecia en la FIG . 2.8

Asimismo aplicando (C) como trada de clock y (A) como entrada po D de un flip flop tipo D se obtiene la señal (E) que también tiene frecuencia del sincronismo vertical y que también tiene una ubicación carac terística con respecto a los pulsos del sincronismo vertical en cada como se observa en la FIG 2.8. Ya que estos pulsos (D) y (E) tienen ubi caciones bien definidas en cada campo los utilizamos con otro flip flop ti po D tal como se ve en la figura 2.7 para definir con la señal (F) la ubicación del primer campo y la del gundo campo.

Esta señal (F) tiene la mitad de la frecuencia del sincronismo vertical

por esto la conoceremos como 2V.

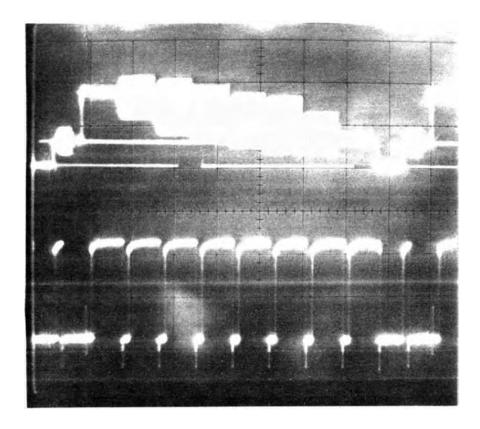

En la figura 2.10 vemos como con  $H_{INT}$  (C<sub>KH</sub>) generado por el contador -910 podemos definir las líneas pares y las impares con respecto a la fase de la subportadora. En la FIG 2.7 esto se realiza con el flip flop 74LS107 cuyas entradas J y K tienen como entradas las subportadora .engan chada, y su entrada de reloj viene a ser  $\mathbf{H}_{\mbox{\scriptsize INT}}$  (o  $\mathbf{C}_{\mbox{\scriptsize KH}})$  con lo cual obtene mos la señal (P) cuya frecuencia es la mitad de la frecuencia horizontal por lo cual la conoceremos como 2H. La señal R viene a ser una división sincrónica de la señal (P) o 2H obtenién dose de esta manera 4H o (R). do en cuenta que cada imagen tiene 525 lineas se obtiene (S) o 4V con un flip flop tipo D tomando como referen cia la fase de la señal P (o 2H) cada imagen.

Se utiliza un monoestable con temporización variable para obtener - una señal de SYNC que pueda ser utili zada para sincronizar el contador de 910. Falta por explicar la función -

de los 3 monoestables de la parte inferior de la figura 2.7 como sabe mos el PLL necesita señales de control para que compare la subportadora con el Burst solamente cuando exista burst. Como sabemos el Burst, por norma, en el sistema NTSC deja de apa recer durante el sincronismo vertical y durante toda la linea activa en ca da linea horizontal. Si durante todo este tiempo ocurre comparación enton ces el PLL creerá que se ha desenganchado y arrojará un voltaje de error grande sin que haya razón para esto. En tonces es necesario crear un pulso de control que nos indique las veces en las que ocurre el Burst. Esto logra con estos 3 últimos monoestables tal como se muestra en el diagrama de tiempos de la figura 2.11 con la señal (A) se dispara un monoestable redispa rable de 46us con esto logramos identificar todo el intervalo de ausencia de Burst. Apartir de los pulsos obte nidos aquí se disparan 2 monoestables uno de 5 us y otro de 3.5us. Elmero ayuda a ubicar el inicio del Burst y el segundo da el tiempo que

dura el Burst, de esta manera obtene mos la señal (K) que nos permitirá realizar el control anteriormente men cionado.

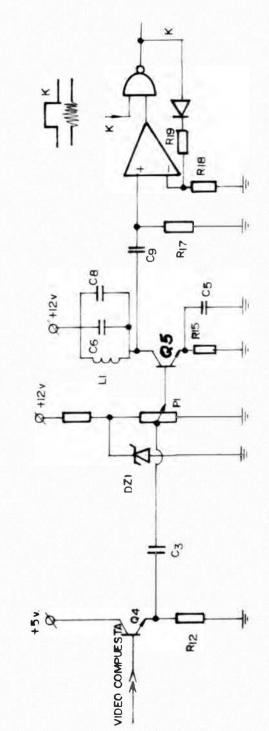

### 2.6 Separador de Burst

A partir de la señal CCVSIN1 que viene de la tarjeta de conversión analógica digital es necesario realizar un circuito que separe el Burst de la señal de video amplificarlo y llevarlo a niveles TTL. Esta señal es el único elemento que tenemos para sincronizarnos con la referencia de la croma de la señal de entrada.

### 2.6.1 Desacoplador de tierras analógica y digital

Como en el caso de la señal SYNC aquí también es necesario realizar una separación de la tierra analógica y de la tierra digital, para que las señales digitales no tengan mucha influencia sobre las señales analógicas. circuito que realiza este desacoplo se muestra en la figura 2.12, se usa la misma técnica que para el circuito del SYNC con la diferencia que aquí se tuvo que realizar este desacoplo en forma discreta, debido a que con el 3051 respuesta en frecuencia que obteníamos era bre, llegando a atenuar bastante la frecuencia de la subportadora y por consiguiente el Burst. Esto nos obligó a realizar un plador como el mostrado donde utilizando sistores que poseen un  $f_{+}$  de 500 MH<sub>2</sub>

mejorar la respuesta en frecuencia y aunque la señal de video aún salía distorsionada el Burst se conservó en buen estado.

## 2.6.2 Separación y amplificación del Burst

En todos los equipos que siguen las carac terísticas del sistema NTSC-M es conocido que el Burst no existe en todas las líneas de una imagen (525 líneas), sino que durante el inter valo vertical el Burst no debe aparecer. En - la fig. 2.8 puede verse claramente cuáles son las líneas en donde el Burst no aparece. La señal K generada convenientemente en la etapa de separación de sincronismos (fig. 2.8) indica los tiempos en los que el Burst se hace pre sente en la señal de video y de la cual nos va lemos para separar el Burst.

El circuito que separa el Burst de la se nal de video y lo amplifica a niveles TTL se muestra en la figura 2.13, se usa una técnica sencilla y de bajo costo para realizar esta acción.

En el circuito mostrado, Q4 es un seguidor de emisor que acopla la señal a tratar.

Luego sigue a través de un amplificador Q5, sintonizado a la frecuencia de la subportadora

DESACOPLO DE TIERRA ANALOGICA Y TIERRA DIGITAL PARA SEPARACION DEL BURST FIG. 2.12

FIG.273 CIRCUITO QUE SEPARA EL BURST

(3.58MHz) de tal manera que se amplifique es pecialmente la parte en que viene el Burst. Des pués sigue el circuito que realiza una amplificación a niveles TTL así como también el con trol mediante el cual se realiza la separación del Burst por medio del pulso K.

En el anexo 1 se muestra el plano del Cir cuito Final de esta etapa.

#### CAPITULO III

#### ETAPA DE CONVERSION ANALOGICA/DIGITAL

#### 3.1 Introducción

Esta etapa es muy importante dentro de lo que es el procesamiento digital de la señal de video. Aquí se realiza la conversión de la señal de video de entrada de analógica a digital. Es decir se conver tirá en una secuencia numérica de tal manera que ésta pueda ser procesada con técnicas digitales.

La exactitud de la conversión es un factor determinante en la buena calidad del procesamiento digital. Para que la conversión sea eficiente y de buena calidad se necesitan fuentes de referencia altamen te estables y circuitos de gran calidad sin olvidar que se debe emplear componentes fáciles de conseguir en el mercado en lo posible.

En esta tarjeta se recibe la señal de video que entra al equipo, luego se la enclava a niveles fi jos, se amplifica la señal y así se la lleva al con versor A/D.

Adicionalmente se regenera el sincronismo - compuesto que luego servirá para obtener las señales requeridas en la etapa de sincronismo.

En consecuencia este capítulo se dedicará - al análisis y diseño de la etapa de conversión analó gica a digital.

## 3.2 Esquema general y diagrama de bloques de la etapa de conversion analógica /digital

Los diversos equipos que podrían conectarse a la entrada del sistema propuesto generan una señal NTSC-M de un voltio p-p para una carga de 50 Ohms. 6 70 Ohms. según sea el caso, por un acuerdo de normalización entre fabricantes.

Sin embargo, la señal de video que entregan va siempre montada sobre un nivel de contínua cuyo va lor varía según el equipo y el contenido de informa - ción.

Para la solución de estos incovenientes es necesario la implementación de un circuito de entrada que permita la adaptación para tener las siguientes - opciones 75 Ohms, 50 Ohms o alta impedancia de entrada que permita aceptar señales de cualquier equipo de TV.

Respecto al nivel de contínua, es necesario incluir un circuito que enclave el nivel de la señal de video a un valor fijo que coloque a la señal dentro del rango de entrada del conversor A/D.

Además, para ocupar todo el rango del con versor y no perder resolución es necesario un amplificador de video donde se pueda controlar la ganacia y el offset de manera que su salida se pueda acoplar

a la entrada del conversor adecuadamente.

El conversor analógico/digital propiamente dicho es la parte más importante de nuestra tarjeta - A/D, y debido a las características especiales del mismo exige la inclusión de fuentes de referencia y de polarización bien fijas y reguladas.

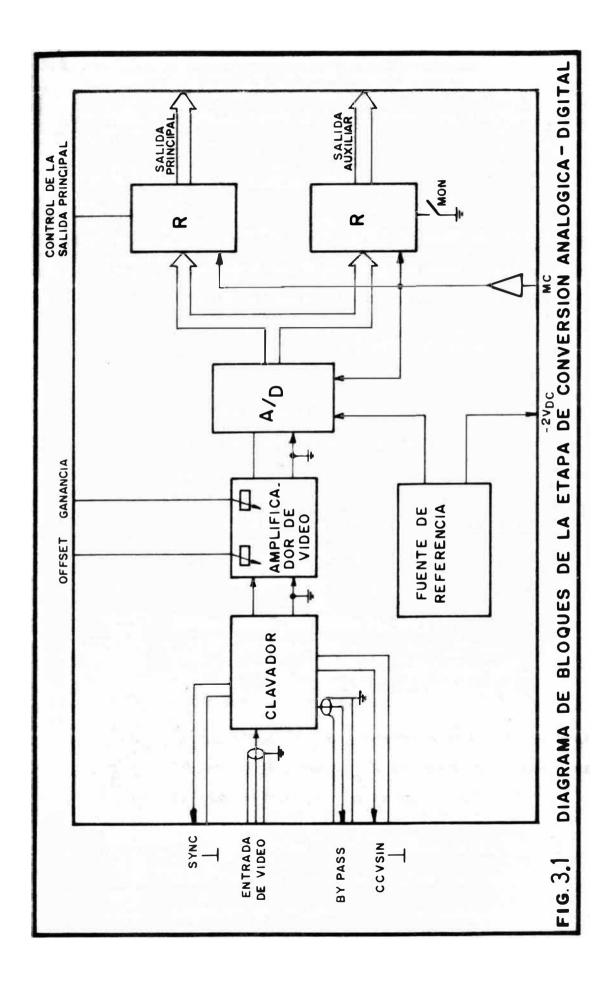

En la figura 3.1 podemos apreciar el diagra ma de bloques resultante. Podemos observar que se han colocado un circuito enclavador de la señal de video, un amplificador de video con controles de ganancia y de offset, el conversor A/D propiamente dicho, las fuentes de referencia que necesita el conversor A/D - para fijar sus niveles de conversión y para la polarización del mismo conversor, y finalmente el arreglo - de los buses de salida de esta etapa: la salida principal y la salida auxiliar.

La salida principal conectará la señal a las siguientes etapas para su procesamiento normal.

La salida auxiliar conecta directamente a la salida del equipo (conversión D/A) para pruebas so lamente y está controlado desde el panel frontal me diante un switch. Adicionalmente en el enclavador se regenera el sincronismo compuesto que será entregado a la etapa de sincronismo (SYNC). La señal CCVSIN es la señal de video compuesta de entrada que se enviará a la etapa de sincronismo para que de ella se pueda separar el burst.

#### 3.3 Circuito de entrada y regenerador de sincronismo

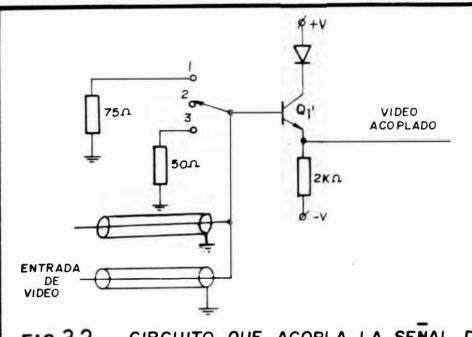

#### 3.3.1 Circuito de entrada

Las opciones para la entrada del equipo - son, como se dijo anteriormente, alta impedan cia de entrada, 75\$6 50\$ por lo cual recurrimos a un circuito seguidor de emisor. Ver figura 3.2.

La impedancia de entrada en la posición 2 viene a ser hfe x  $2K \preceq 3M \Omega$ . Con el selector se puede escoger la impedancia de entrada.

El diodo evitará el flujo de corriente de fuga del colector del transistor Q.

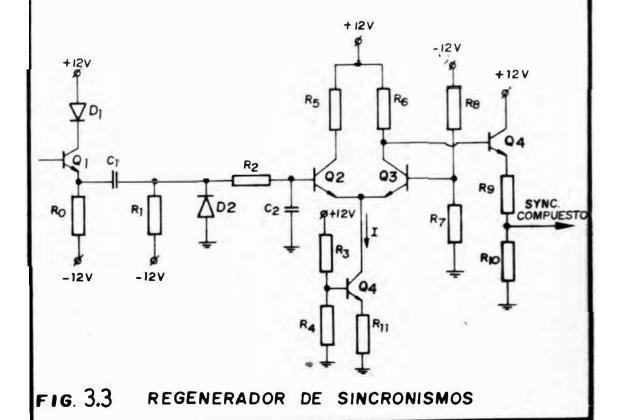

#### 3.3.2 Regenerador de sincronismos

En este momento es adecuado realizar la regeneración del sincronismo ya que nos po demos valer de este circuito para realizar par te del enclavador. El esquema que usamos es - el que se muestra en la FIG. (3.3).

Para tener alta impedancia de entrada y no cargar la etapa de entrada se coloca este - seguidor de emisor, que consiste en el diodo D1, el transistor Q1 y la resistencia RO. El diodo D1 sirve para evitar la corriente de fuga

FIG. 3.2 CIRCUITO QUE ACOPLA LA SENAL DE VIDEO AL EQUIPO

ICBO.

El valor de RO se ha calculado de manera que la impedancia de entrada sea alta pero no tanto como para aumentar la capacidad de entra da.

$$RO = {^{Z}in}$$

=  $RO = 2K$

C<sub>1</sub> y D2 conforman un circuito enclavador del nivel más bajo de la señal de video en -0.6V.

Los transistores Q2,Q3 y Q4 y resistencias R5,R6,R3,R4 y R11 implementan un comparador que compara un nivel fijo dado por R7 y R8 en -0.3V aproximadamente y la señal de video ya enclavada en -0.6V.

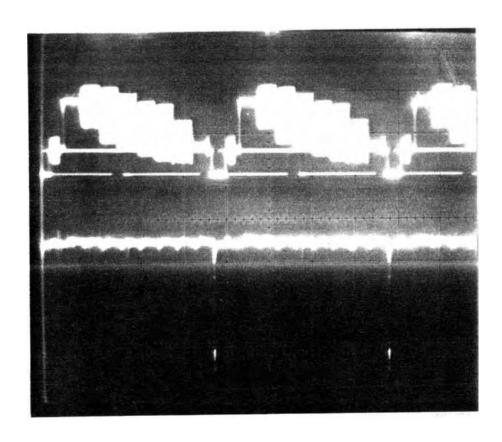

En el colector de Q3 se obtiene la señal de sincronismo compuesto. La FIG 3.4 muestra como lo realiza.

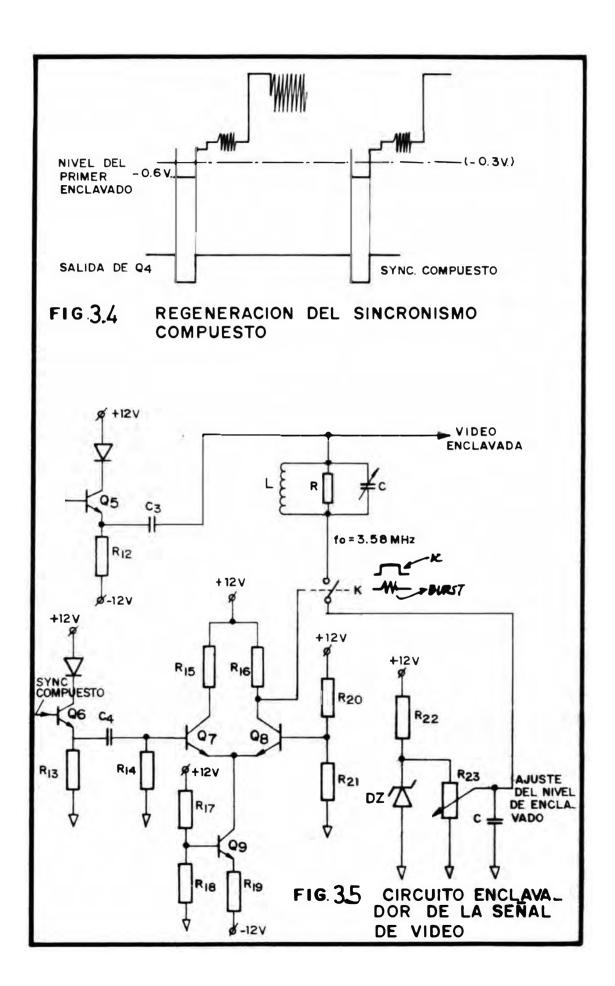

#### 3.3.3 Enclavador

El nivel supresión sobre el cual el burst va montado es un buen punto de referencia para enclavar la señal de video.

El circuito utilizado se muestra en la FIG. 3.5. Este circuito retarda el pulso de sincronismo creando una serie de pulsos cuya -

ubicación, esta sobre el burst y luego estos - pulsos se cuadran con el comparador formado por Q7,Q8 y Q9. Este pulso, que se obtiene en el colector del transistor Q8 gobernará el con trol de una puerta CMOS 4016. El diodo zener D2 y las resistencias  $R_{22}$  y  $R_{23}$  constituyen una fuente de referencia ajustable y bastante precisa. El circuito RLC está sintonizado a la frecuencia de la subportadora.

Cada vez que ocurre el burst, el pulso

"K" (ver FIG. 3.5) cierra el conmutador CMOS

y el circuito sintonizado deja pasar la ten

sión continua de referencia, pero no así el

burst, ya que para este, el tanque se comporta

como un circuito abierto. Por consiguiente ca

da vez que ocurre el burst se actualiza el ni

vel de supresión con la tensión DC de salida de la fuente de referencia.

Por práctica, se sabe que la constante de tiempo del enclavador debe ser menor que 4 ve ces el período de una línea horizontal. Esta constante es el tiempo que demora en fijar una señal de video después, de una variación brus ca de su nivel de tensión contínua. Un tiempo mayor podría ser detectado por el ojo humano, esta constante esta dada por.

$$T = C_3 \times R_{(RLC + Vref)}$$

Las variaciones de la tensión Vref con la temperatura son mínimas al utilizar un zener - cuyo voltaje esté en el orden de los 5 a 6 vol tios. El potenciómetro  $R_{23}$  nos permite el a juste de la tensión de referencia del enclavador.

### 3.4 Amplificador de video

El conversor analógico digital tiene un ran go de entrada de 2V. Se trata de aprovechar todo el rango de entrada para ganar buena resolución con el conversor. Esta etapa se encarga de amplificar la señal de video, enclavada por la etapa anterior, de un voltio pico a pico a 2 voltios pico a pico.

### 3.4.1 Especificaciones

a.- La ganancia requerida en este caso es 2, para obtener 2 voltios pico a pico con una entrada de 1 voltio pico a pico.

b.- La respuesta del amplificador debe ser pla na en el rango de O a 4.5 MHZ para una carga - de 300 pico faradios en paralelo con 5000 Ohm., que viene a ser la impedancia de entrada del - conversor A/D propiamente dicho.

c.- El circuito deberá poseer posibilidades para calibrar el offset asi como también la ga-

#### 3.4.2 Implementación

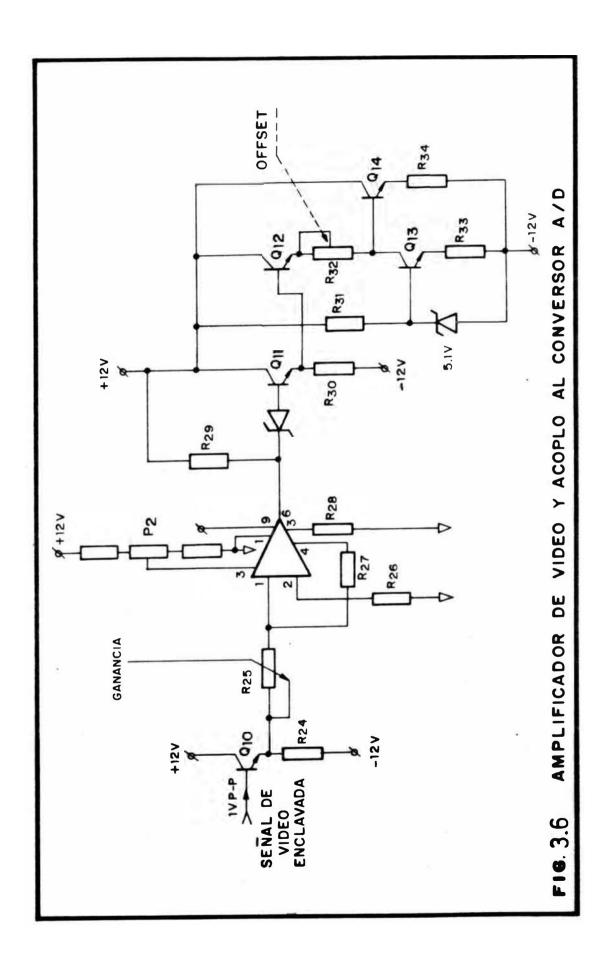

La configuración utilizada se muestra en la FIG. (3.6). Después de probar una serie de

esquemas llegamos a la implementación de un circuito híbrido constituido con un amplifica dor integrado ICl (MC 1550) y otros elementos discretos para acoplo de la señal de video con las siguientes etapas y el desplazamiento del nivel de contínua (control de offset).

El integrado MC 1550 es un amplificador - de RF e IF, que se usa bastante en equipos de comunicaciones. El mismo posee un termina\_ - AGC, pudiéndose por lo tanto realizar el ajuste de la etapa, mediante el potenciómetro P2.

Un defecto de este amplificador es que posee un offset bastante alto, alrededor de 9V DC. En este punto la señal ya esta amplificada a 2V pico a pico pero aún no puede ser aplicada al conversor.

El circuito siguiente, sirve para acoplar con alta impedancia de entrada y baja impedancia de salida la señal de video del amplificador al conversor, pero a la vez también baja el nivel DC de salida del amplificador a niveles tolerables por el conversor A/D.

El diodo DZ1 baja el nivel de DC con un coeficiente de temperatura reducido. El tran sistor Q11 es un driver que acopla la salida - del MC 1550, los transistores Q12 y Q13 bajan

el nivel hasta 0.7V y se acopla al conversor - A/D con un driver para salir con baja impedancia.

## 3.4.3 Resultado experimental

Se midió una caída de poco menos de 1dB en el rango de O a 4.5 MHz.

#### 3.5 Conversor analógico digital

La etapa de conversión analógica a digital incluye al circuito conversor A/D propiamente dicho - y las fuentes de referencia utilizadas para dar mayor presición a la conversión.

Esta es la parte circuital que se encargará de convertir la señal de video NTSC en una secuencia numérica organizada en una serie de palabras binarias de 8 bits cada una, apartir de ese momento podrán procesarse dichos datos numéricos.

#### 3.5.1 Especificaciones

El conversor A/D utilizado deberá sopor - tar los siguientes requerimientos para una bue na calidad de conversión de la señal de video:

Resolución 8 bits

Frecuencia de conversión 14.3 MHz

Error menos que  $\frac{+}{2}$  1 bit (LSB) pico a pico

Ancho de banda mayor que 4.2 MHz

Relación señal a ruido (6N + 1.8)

dB = 49.8dB para N = 8 bit

Independencia entre tierra digital y ana-

lógica

Pequeño

Bajo costo

#### 3.5.2 Implementación

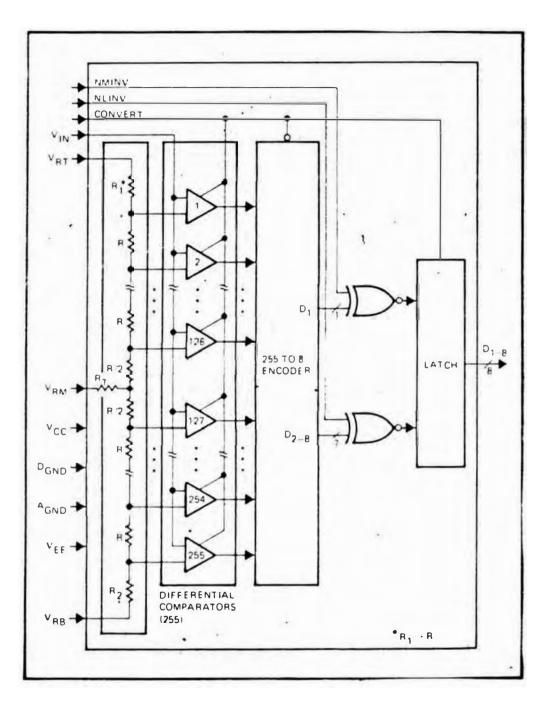

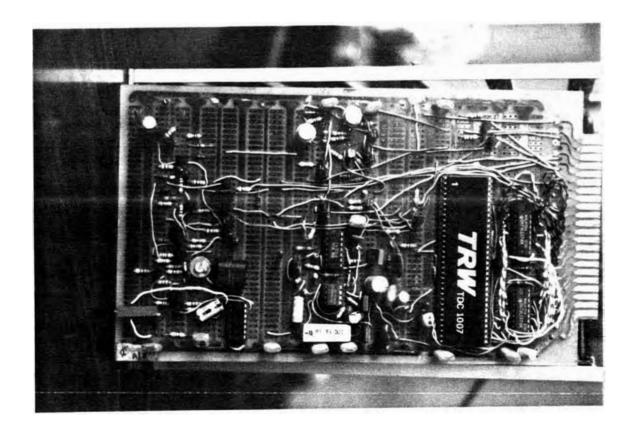

El que en la actualidad satisface estas - condiciones el el TDC 1007J el cual utilizamos en nuestro equipo. El mencionado circuito es un híbrido monolítico constituído por 255 comparadores, resistencias de presición, encoder y registros organizados como latches.

En el apéndice se detallan las caracterís ticas de este conversor. En la figura 3.7 se muestra el diagrama circuital de este conver - sor.

Las entradas NMINV y NLINV, servirán para seleccionar la polaridad de la señal de en trada con respecto al nivel digital 0000. A la entrada CONVERT llegará el MASTER CLOCK (14.3 MHz) quién dará la cadencia para la conversión al cuádruplo de la frecuencia de la subportado ra.

Vin, es el pin por donde ingresa la señal de video, su rango de entrada es desde OV

HASTA -2V,VRT y VRB, son las entradas para las fuentes de referencia que determinan los extre mos del rango de voltaje de entrada que podrá

FIG. 3.7 ESQUEMA DEL CONVERSOR A/D TDC1007J

ser cuantificado (VRT = OV, VRB = -2V) VRM modifica la ley de cuantificación, en nuestro caso se deja al aire, no se usa.

Los peines  $D_1$  al  $D_8$  son las salidas de da tos digitales y Vcc y VEE son conexiones para la alimentación de +5V y -6V respectivamente. Su potencia disipada llega a 2W.

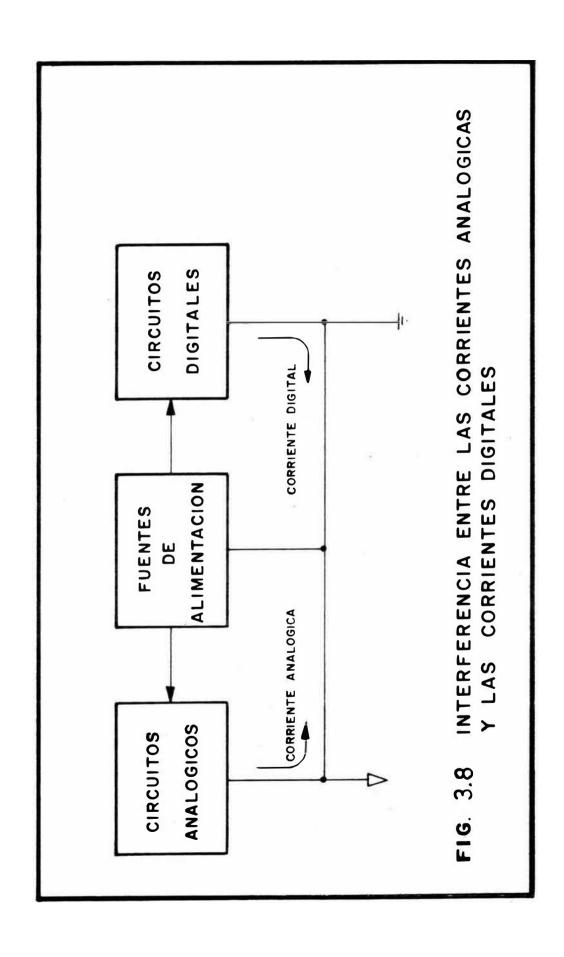

# 3.5.3 <u>Consideraciones sobre las tierras analógica y</u> digital

Las entradas DGND y AGND del conversor TDC 1007J corresponden a las tierras digital y analógica respectivamente. Es muy importante considerar que los caminos de retorno de las - corrientes de las señales analógicas y digitales deben ser independiente en lo posible. Si la tierra fuera única, ambas corrientes, la de la señal digital y la de la señal analógica, se interferirían y la última sería la más afectada. En la FIG. 3.8 se trata de mostrar en un esquema lo anteriormente explicado.

En el anexo 2 se muestra el plano del cir cuito final de esta etapa.

#### CAPITULO IV

#### FILTRO PASA BAJO/PASA ALTO

## 4.1 Introducción

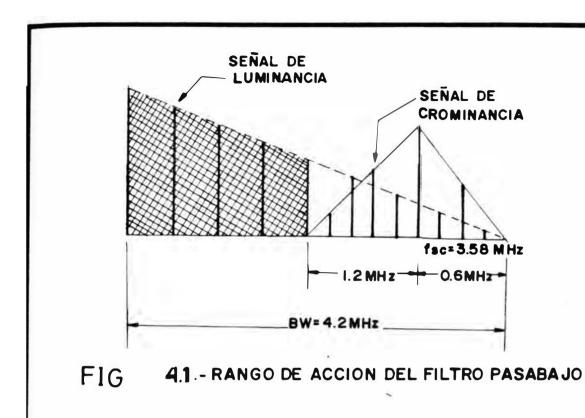

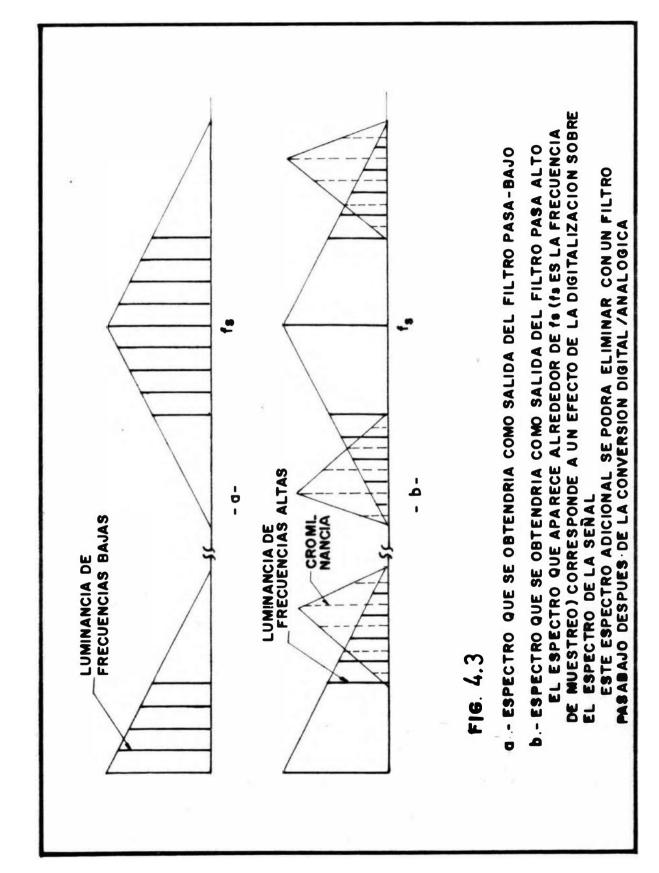

La realización de esta etapa está intimamen te ligada con el método utilizado para la separación de la luminancia y la crominancia; el método en cues tión consiste en separar la luminancia y la crominancia utilizando un filtro digital denominado "Filtro Peine". La utilización del filtro peine causa cierta pérdida de resolución vertical (esto se explicará con más detalle en el siguiente capítulo), entonces el filtro pasa bajo/pasa alto servirá para limitar el efecto del filtro peine a la zona del espectro de fre cuencia en la que predomina la crominancia, tal como se muestra en la FIG. 4.1, reduciendo así efectos nega tivos del filtro peine sobre la señal de video.

El presente capítulo, tratará aspectos referentes a la concepción, diseño y problemas en la implementación circuital indispensables para realizar un filtro apropiado de la señal de video, sin menos cabo de su calidad.

## 4.2 Concepción y diagrama de blocues

Esta tarjeta cumple un papel muy importante en el proceso de separación de los componentes LUMI - NANCIA y CROMINANCIA de la señal de video.

Ha sido concebida como parte del proceso de separación de manera que reduzca los efectos del filtro peine a la banda de frecuencias en la que domina la crominancia; por lo tanto esta deberá una serie de requerimiento mínimos.

### 4.2.1 Requerimientos mínimos

a) ANCHO DE BANDA:  $(BW_{FPR})$

$$BW_{FPB}^{}=BW$$

total - BW crominancia  $BW_{FPB}^{}=4.2$  MHz - 1.8 MHz = 2.4 MHz

- b) El filtro debe ser un filtro digital y de be tratar con la señal de video en forma de una secuencia numérica digital. Cada uno de estos números en esta secuencia tiene una re presentación binaria en palabra de 8 bits y en aritmética complemento a dos es decir que el bit más significativo da el signo a los 7 bits menos significativos que constituyen el -valor absoluto de la señal en ese punto.

- c) Los valores máximo y mínimo que puede tomar

un número en la secuencia numérica anterior mente mencionada son:

Nivel + valor máximo 11111111

Nivel - valor minimo 00000000

- d) Deberá poder tratar con una secuencia numérica que avanza con una velocidad de 14.3 MHz ya que esta es la frecuencia a la cual se efec túa la conversión Analógica/Digital. Este da to es importante ya que hablamos de un período de 70 nanosegundos aproximadamente que es un tiempo que esta relativamente cerca a la res puesta de algunos componentes TTL que son los que se usarán en este diseño.

- e) Para el filtro se deberá considerar una con figuración que proporcione un retardo de grupo, constante en todas las frecuencias del espec tro de la señal de video. Este requerimiento es muy importante y esta íntimamente relaciona do con la calidad final de la señal. Si el retardo de grupo no fuese constante en todo el ancho de banda de video se produciría en la pantalla de televisión deformación de la ima gen, así como desplazamiento de los colores so bre las mismas. Asimismo una buena respuesta en amplitud.

- f) Se deberá considerar la derivación del fil-

tro pasa alto de manera que por esta salida obtengamos la salida de la banda correspondiente a crominancia y luminancia de las frecuencias más altas del ancho de banda de video.

g) Se considerará una salida auxiliar del fil tro pasa alto, que esté dirigida hacia el bus de prueba y que pueda ser manejada (Habilitada o no Habilitada) desde el panel frontal.

#### 4.2.2 Diagrama de bloques

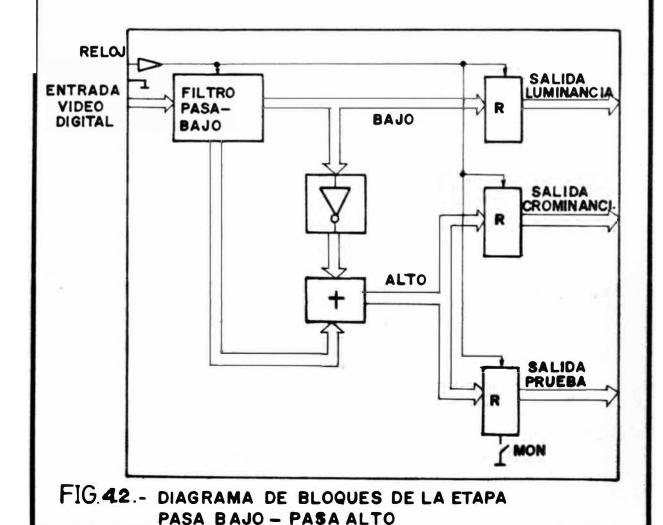

En la FIG. 4.2, se muestra el diagrama de bloques que representa las características re queridas en la etapa pasa bajo/pasa alto. Se aprecia como entradas de la tarjeta a la señal de video digitalizada y una señal que da la cadencia o velocidad de procesamiento.

Esta señal ingresa al filtro pasa bajo y sale hacia las siguientes etapas a través re gistros 74LS374, ésta salida constituye la sa lida de luminancia que pasa por el filtro pasa bajo.

Por otro lado se realiza el complemento de la respuesta del filtro pasa bajo, dando lu

gar a la salida del filtro pasa alto, por don

de se obtiene la señal de crominancia mezclada

con la señal de luminancia de las frecuencias altas del espectro de video. Esto se realiza trabajando en aritmética complemento a dos; efectuando una resta entre la salida del pasa bajo y la señal total se obtiene la respuesta del pasa alto. En la FIG 4.3 se muestra un dibujo esquemático de los espectros que se ob tendrán en las salidas del PASA BAJO y del PASA ALTO.

#### 4.3 Diseño del filtro

# 4.3.1 Elección de la configuración

Entre todos los requerimientos mínimos im puestos para el diseño de esta etapa el que tiene que ver directamente con la elección del tipo de filtro corresponde al que se refiere - al "retardo de grupo".

El retardo de grupo debe ser constante, para todas las frecuencias del ancho de banda

de la señal de video. Asimismo se desea una

buena respuesta en amplitud.

Como sabemos básicamente existen dos ti pos de filtros digitales, los filtros de res puesta impulso infinita (IIR) y los filtros de respuesta de impulso finito (FIR).

Los primeros, los filtros IIR, son aque llos que presentan una función de transferen - cia racional y son los comúnmente conocidos co mo filtros recurrentes, debido a que su cálculo requiere utilizar un algoritmo computacional - recursivo. Los filtros FIR en cambio tienen una función de transferencia polinominal y co munmente son denominados como filtros "no-recurrentes" ya que el algoritmo utilizado para

determinar los coeficientes de la función de transferencia es no-recursivo.

Con los filtros digitales del tipo IIR se mejora la respuesta en amplitud a costa de pe $\underline{r}$  der linealidad en la respuesta de fase.

En cambio los fitros digitales del tipo FIR se utilizan cuando se desea tener fase com pletamente lineal y al mismo tiempo una buena respuesta en amplitud pero sacrificando en - el Hardware ya que para este último se necesita más elementos que con el anterior.

El requerimiento de retardo de grupo cons tante es fundamental en la elección del tipo de filtro a usar, es por este motivo que los filtros del tipo FIR son apropiados para la presente aplicación.

Con este tipo de filtro podemos obtener un retardo de grupo constante, o en otras pala bras una respuesta de fase lineal, para ancho de banda bastante extensos. Si estos filtros son implementos con componentes TTL el ancho de banda de la respuesta de fase lineal se prolonga más allá de los 15 MHz.

Por otro lado, los filtros FIR brindan las ventajas de poder usar algoritmos rápidos

como la transformada rápida de Fourier, para la cual es imprescindible una respuesta impulso finita la cual es inherente a los filtros FIR.

### 4.3.2 Diseño

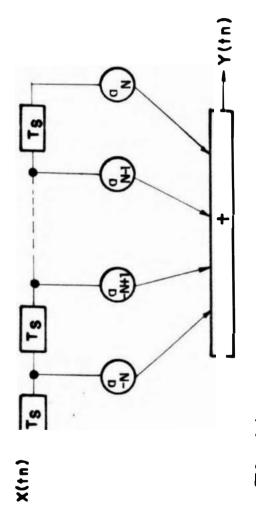

La FIG 4.4, muestra el diagrama de bloques del filtro transversal el cual nos va a permi - tir determinar la función de transferencia con un cálculo muy breve:

La señal de salida Y(tn) =

$$\sum_{-N}^{N} a_{K} \times (tn-Kts)$$

(1)

La función de transferencia es la transformada a la salida si la entrada es la función impulso. En este caso la salida es:

$$h(tn) = \sum_{-N}^{N} a_k \delta(tn - kts)$$

(2)

Tomando transformada tenemos:

$$H(e^{jw}) = \sum_{-N}^{N} a_k e^{-jkwts}$$

(3)

Para garantizar fase lineal hacemos

$$a_{-k} = a_k \tag{4}$$

Reemplazando (3) se reduce a

FIG44: DIAGRAMA DE BLOQUES DE UN FILTRO TRANSVERSAL NO RECURRENTE

$$H(W) = \sum_{-N}^{N} a_k \cos kwts$$

Después de una serie de cálculos e intentos se llegó a determinar con cinco elementos una respuesta aceptable.

Calculando para cinco elementos.

$$H(w) = 2 \propto \frac{1}{4} \cos 4wt_s + 2 \propto \frac{1}{3} \cos 3wt_s + 2 \propto \frac{1}{2} \cos 2wt_s + 2 \propto \frac{1}{1} \cos wt_s + \propto 0$$

Asignando valores a algunos puntos de la curva

$$H(w = 0) = 2\alpha_4 + 2\alpha_3 + 2\alpha_2 + 2\alpha_1 + \alpha_0 = 1$$

(1)

$$H(w = 11/6) = - \times_4 + \times_2 + \sqrt{3} \times_1 + \times_0 = 1$$

(2)

$$H(W = 11/3) = - \chi_4 - 2 \chi_3 - \chi_2 + \chi_1 + \chi_0 = 1/2$$

(3)

$$H(W + \Pi/2) = 2 \times 4 - 2 \times 2 + 2 = 0$$

(4)

maniobrando con las expresiones obtenidas:

$$(1) - (4): 2\alpha_3 + 4\alpha_2 + 2\alpha_1 = 1$$

(5)

(2) (3):

$$2 \propto_3 + 2 \propto_2 + (\sqrt{3} - 1) \propto_1 = 1/2$$

(6)

(5) - (6):

$$2 \alpha_2 + (3 - \sqrt{3}) \alpha_1 = 1/2$$

Simplificando

$$\alpha_2 = \frac{1}{4} - \frac{3 - \sqrt{3}}{2} \alpha_1$$

(7)

(5) en (2-3)

$$2 \frac{1}{3} + \left[ \frac{1}{2} - (3 - \sqrt{3}) \frac{1}{2} \right] + (\sqrt{3}^{1} - 1)$$

$\frac{1}{2} = \frac{1}{2}$

Simplificando

$$\alpha_{3} = (2 - \sqrt{3}) \alpha_{1}$$

(8)

$$(4) + 2x(2) \quad 2\sqrt{3}\alpha_{1} + 3\alpha_{0} = 2$$

Simplificando

(7) y (9) en (2)

$$-\alpha_{4} + \left[\frac{1}{4} - \left(\frac{3 - \sqrt{3}}{2}\right)\alpha_{1}\right] + \sqrt{3}\alpha_{1} + \left[\frac{2 - 2\sqrt{3}}{3}\alpha_{1}\right]$$

$$= 1$$

Simplificando

Reemplazando (7), (8), (9), (10) en H(w) tenemos:

$$H(w) = 2(\frac{1}{6}(5\sqrt{3} - 9) \propto 1 - \frac{1}{12}) \cos 4wts +$$

$$2((2 - \sqrt{3}) \propto 1) \cos 3wts +$$

$$2(\frac{1}{4} - \frac{3 - \sqrt{3}}{2} \propto 1) \cos 2wts +$$

$$2 \propto 1 \cos wts +$$

$$\frac{2}{3} - \frac{2\sqrt{3}}{3} \propto 1$$

(11)

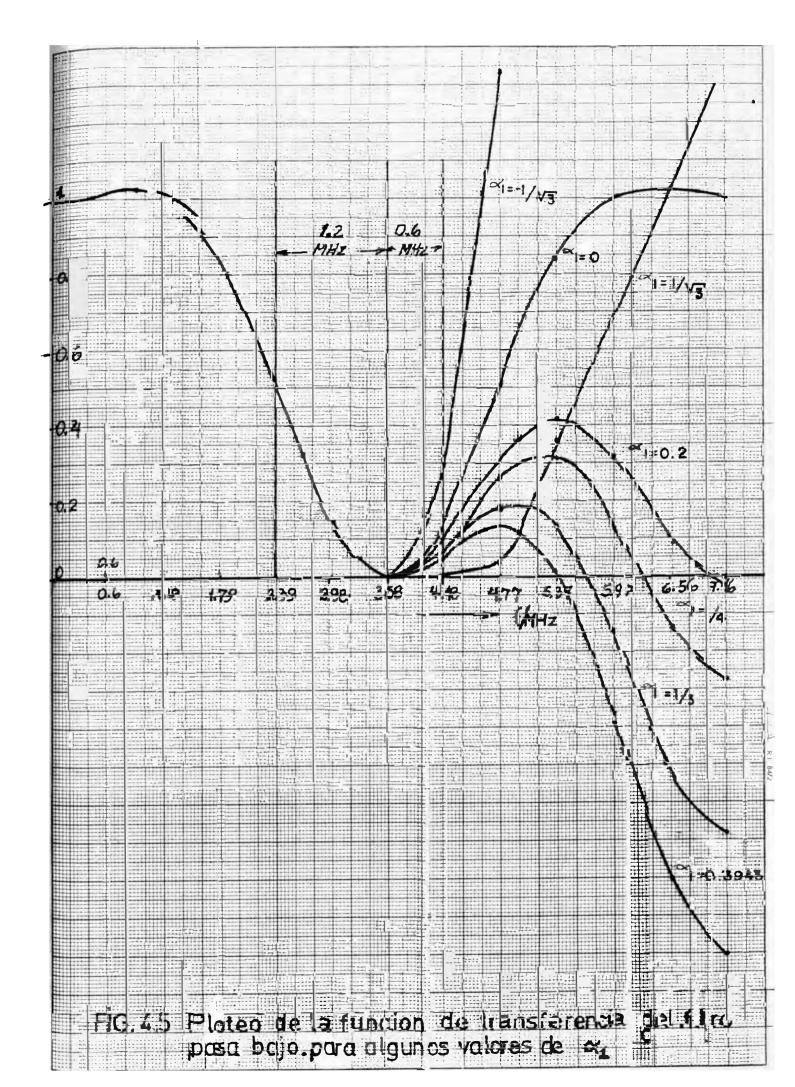

En la ecuación (11) tenemos la respuesta - del filtro en función de pprox  $_1$ . De este modo va riando el parámetro pprox  $_1$  obtendremos una familia de curvas de la cual escogeremos la mas apropia da.

En la figura 4.5 aparece el ploteo de la - ecuación (11) para diferentes valores de $\alpha$ .

Después de hacer una inspección de las di ferentes curvas se ha escogido la correspondien te a  $\alpha_1$  = 0 por los siguientes motivos:

El coeficiente  $\alpha_1 = 0$  hace que los demás coeficientes sean fáciles de implementar.

Esta curva posee un rizado menor que 2% dentro del ancho de banda del video.

La función de transferencia resultante es:

$$H(w) = -\frac{1}{6}\cos 4wts + \frac{1}{2}\cos 2wts + \frac{2}{3}$$

(12)

En la figura 4.6 podemos apreciar en mayor detalle las características de respuesta en am plitud del filtro escogido y su correspondiente para el pasa alto.

La zona sombreada corresponde al dominio - de la crominancia; puede observarse que se

espera que hayan residuos de crominancia en la zona correspondiente a la salida del pasa bajo y también residuos correspondientes a la lumi - nancia quedarán en la zona que idealmente co rresponde a la crominancia.

## 4.4 Implementación del filtro

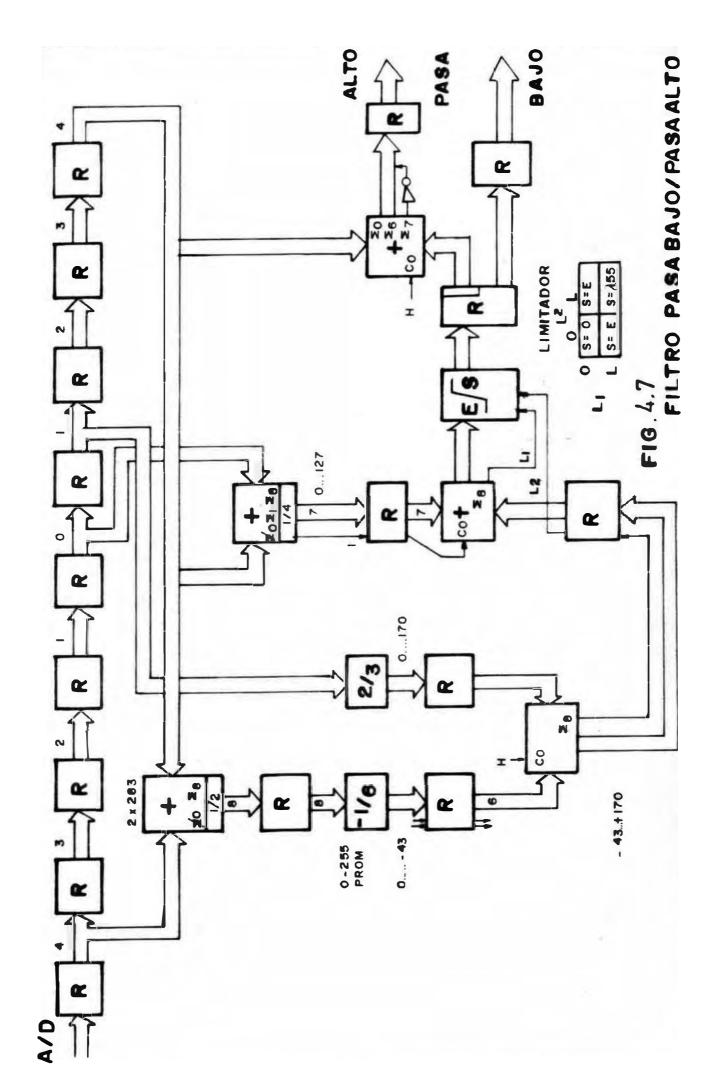

En la figura 4.7 se muestra el diagrama es quemático del circuito para el filtro pasa bajo/pasa alto.

El circuito consiste en la realización de la ecuación resultante de los cálculos (ecuación 12) con circuitos lógicos. En este caso cada registro de la parte superior de la figura es un elemento de retardo de aproximadamente 70 nanosegundos. Los coe ficientes - 1/6 y 2/3 de la ecuación 12 se han realizado con tablas grabadas en memorias prom. En la sa lida del filtro pasa bajo se ubicó un limitador digital de amplitud para evitar que el resultado salga del rango de 0 a 255. Luego se toma esta salida y con lógica de aritmética en complemento a dos se obtiene la respuesta del filtro pasa alto.

En el apéndice se encuentran las tablas para grabar los coeficientes - 1/6 y 2/3 de la ecuación (12).

En el anexo 3 se encuentra el plano del cir cuito final del filtro pasabajo/pasa alto.

#### CAPITULO V

#### ETAPA FILTRO PEINE

#### 5.1 Introducción

Desde la introducción de la televisión a color hace unos 30 años, ha habido un esfuerzo continuo por mejorar la performance y características de los equipos involucrados con la señal de televisión a color. Como resultado de estas investigaciones tenemos que el FILTRO PEINE, que ya se conocía por varias décadas, hace posible su aplicación en el diseño de circuitos de televisión a color a través de los avances en las técnicas de fabricación de los ahora famosos "Dispositivos de acoplo de carga" y de los circuitos integrados.

La aplicación del filtro peine en el diseño de los circuitos de televisión, es muy ventajosa ya que permite mejorar la resolución de imagen y librar-la de la interferencia entre las señales de luminan -cia y crominancia.

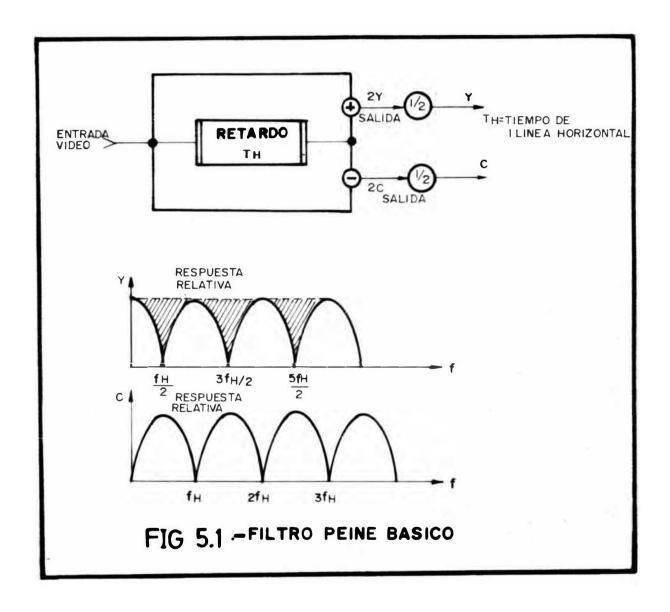

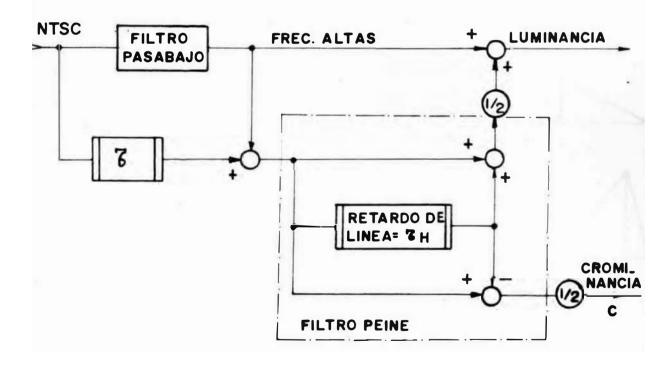

El filtro peine básicamente es un tipo filtro transversal el cual puede ser usado para separar eficientemente Y (LUMINANCIA) y C (CROMINANCIA) señal de video compuesta NTSC; la característi ca importante que le permite realizar esto es su puesta en frecuencia periódica, la cual contiene giones pasabanda, que cuando es ploteada en una gráfi ca se parece a los dientes de un PEINE. En la figura 5.1 se muestra la configuración que producirá las dos características complementarias necesarias para la separación de luminancia y crominancia de una ñal de video compuesta NTSC y en la figura 5.2 se pue de apreciar, asimismo la característica del espectro de frecuencias de la señal de video NTSC. Esta carac terística especial en forma de líneas en el cual líneas del espectro de crominancia están entrelazadas a las del espectro de luminancia hace que el filtro peine se constituya como un separador eficiente de es tos componentes.

Esta etapa viene a ser la más importante dentro de lo que es el proceso de separación, de los componentes de luminancia y crominancia. Asimismo es tá intimamente ligada con la etapa analizada en el ca pitulo anterior, FILTRO PASA BAJO/ALTO ya que conjuntamente con esta se realiza una separación eficiente de los componentes de la señal de video.

# 5.2 Concepción y diagrama de bloques

## 5.2.1 Cálculo del retardo del filtro peine:

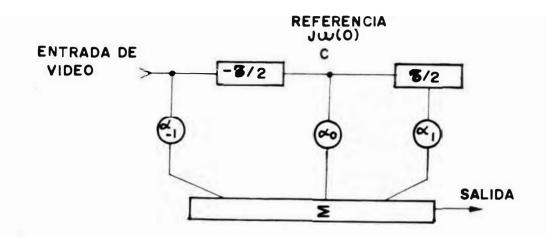

El filtro peine básicamente es un tipo de filtro transversal. En la figura 5.3 se muestra el esquema de un filtro transversal típico con dos elementos de retardo. Aquí  $x_0$ ,  $x_1$   $x_{1}$  son los coeficientes del filtro y  $x_1$  es el retardo.

Por consiguiente la ecuación del filtro resulta ser:

$$H(w) = \frac{w\tilde{v}}{2} + \frac{w\tilde{v}}{2} + \frac{w\tilde{v}}{1} e$$

(1)

$$H(w) = \alpha_{-1} \left(\cos \frac{w\mathcal{T}}{2} + i \operatorname{sen} \frac{w\mathcal{T}}{2}\right) + \alpha_{0} + \alpha_{1} \left(\cos \frac{-w\mathcal{T}}{2}\right)$$

$$+ i sen \frac{-W\overline{7}}{2}$$

) (2)

si escogemos

$$\alpha_0 = 0$$

$$\alpha_1 = \alpha_{-1} = 1 \text{ obtenemos:}$$

$$|H(w)| = 2 \cos \frac{wZ}{2}$$

(3)

En el caso de la respuesta complementaria esco gemos:

$$\mathcal{X}_0 = 0$$

$\mathcal{X}_1 = 1$

$\mathcal{X}_{-1} = -1$  obtenemos:

$$H(w) = 2 \operatorname{sen} \left(\frac{W\overline{\ell}}{2}\right) \tag{4}$$

Observando la figura 5.1 vemos que para que (3) y (4) correspondan a las funciones necesarias para separar la luminancia y la crominancia, se debe cumplir lo siguiente:

Teniendo en cuenta la figura5.2, en la ecuación (4), H(w) debe tener un máximo en múl tiplos de la frecuencia horizontal. De este - modo se podrá separar la crominancia.

Por consiguiente cos (wZ/2) = 1 en  $w = 2 \pi f_h$  (5)

a la frecuencia horizontal  $w = 2\pi f_h$  (6)

de (5) y (6)  $\pi = w / 2$

$\pi = 2 \pi f_h \frac{\mathcal{E}}{2}$ Por lo tanto  $\mathcal{E} = T_H$ (7)

Haciendo una breve inspección se ve que este - retardo calculado vale para las funciones (3) y (4).

En la figura 5.4 se muestra el filtro pe<u>i</u>

ne con sus dos salidas L y C que conjuntamente

con el filtro pasa bajo hará una separación

FIG. 5.3 - ESQUEMA DE UN FILTRO TRANSVERSAL CON 2 ELEMENTOS DE RETARDO

FIG. 5.4 FILTRO PEINE

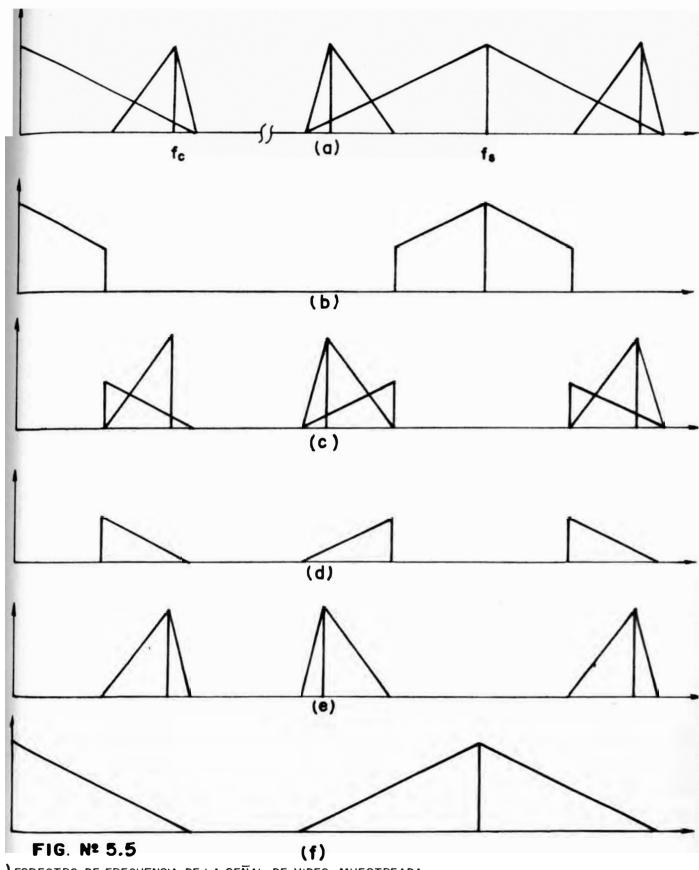

- ) ESPECTRO DE FRECUENCIA DE LA SENAL DE VIDEO MUESTREADA

- (b) LUMINANCIA DESPUES DE PASAR POR EL FILTRO PASABAJO

- (c) LUMINANCIA + CROMINANCIA DESPUES DE PASAR POR EL FILTRO PASA ALTO

- (d) SALIDA LUMINANCIA DEL FILTRO PEINE

- ( )SALIDA CROMINANCIA DEL FILTRO PEINE

- (1) RECONSTRUCCION DE LA LUMINANCIA TOTAL

eficiente de los componentes luminancia y crominancia.

En la figura 5a el espectro de la señal - de video compuesta tiene espectros imágenes al rededor de múltiplos de la frecuencia de muestreo. El proceso de separación se inicia con el filtro pasa bajo (fig. 5b) y el filtro pasa alto (fig. 5c). Con la salida de este último fig. (5c) se realiza la verdadera separación - con el filtro peine obteniéndose las salidas - crominancia (fig. 5c) y luminancia (fig. 5d) esta última al sumarse a la salida del filtro pasa bajo (fig. 5b) reconstituye a la señal de luminancia.

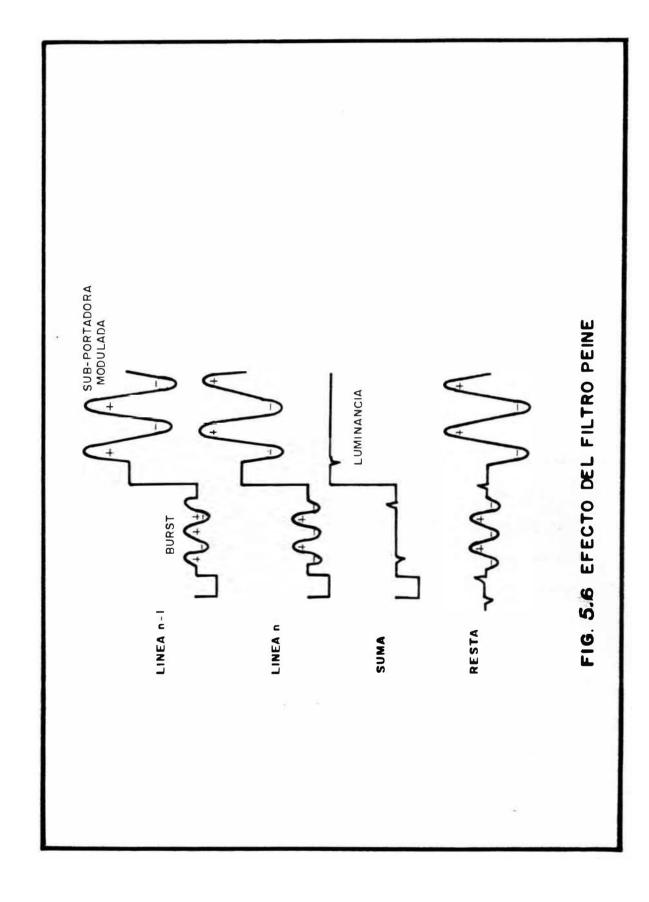

#### 5.2.2 Diagrama de bloques:

La función del filtro peine puede enten - derse mejor observando el circuito de la figura 5.4 y teniendo en cuenta la secuencia de la - figura 5.6. En principio aprovecha la correla - ción de la información en dos líneas consecuti vas de la imagen de video. El elemento principal del filtro peine es una memoria para retar dar la señal exactamente el tiempo de una línea horizontal. En el punto de adición donde se junta la señal actual y la señal retardada se duplica el componente de luminancia y se

elimina la crominancia debido a que la fase de la subportadora es opuesta en dos lineas conse cutivas. La frecuencia de la subportadora de NTSC es un impar múltiplo de la media frecuencia horizontal.

$$f_{sp} = f_h (2n + 1)/2; n = 227$$

En el punto de sustracción ocurre lo contrario, la diferencia de las señales actual y retardada solo contiene la crominancia, se elimina la luminancia por que es idéntica (aproximadamente) en dos líneas consecutivas.

Aunque la combinación de la información - de líneas consecutivas significa una reducción de la resolución vertical, este efecto no es tan importante para la crominancia como lo es para la luminancia. Para la luminancia este efecto no es deseado ya que esto disminuye la nitidez vertical de la imagen. Este efecto negativo ha sido reducido limitando el efecto del filtro peine para las altas frecuencias de la señal compuesta por medio del filtro pasa bajo tratado ya en el capítulo anterior.

Para las frecuencias bajas (solo luminancia) se realiza un desvío y el efecto del filtro peine repercute en el rango de la mezcla de los dos componentes.

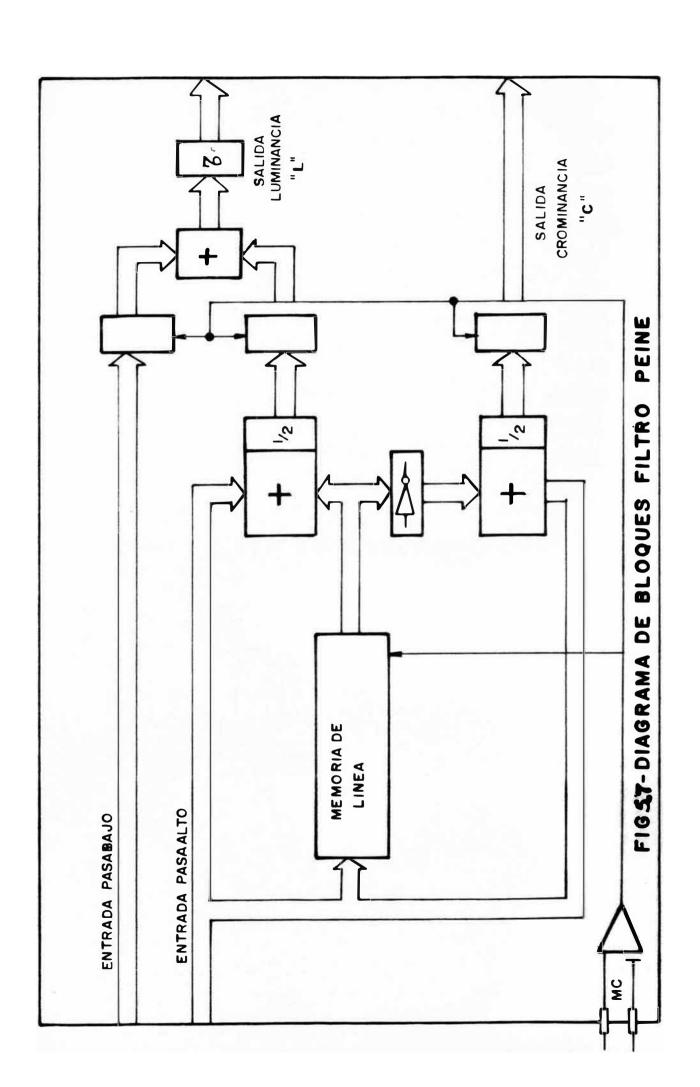

### 5.3 Implementación circuital

En el área de un procesamiento digital, el filtro peine se realiza con elementos de retardo (re gistros y memorias) y sumadores.

En la figura 5.7 se muestra el esquema circui tal a nivel de bloques de la implementación del filtro peine. En esta figura falta definir la memoria de retardo y el circuito de control de la misma, que tienen la función de lograr el retardo de la señal por el tiempo de una línea. La velocidad con que aparecen las muestras de la señal de video 14.3 MHz esdecir cada 70 ns aproximadamente, hace que el requerimiento para el tiempo de acceso de las memorias a uti lizar sea de 35 ns es decir 35 ns de lectura y 35 ns de escritura. En este caso se tendrá una sola memoria de retardo de línea con capacidad para almacenar el número de muestras que hay en una línea, es decir, 910 muestras.

Sin embargo este requerimiento puede ser me nos exigente si utilizamos dos memorias de la misma - capacidad en una de las cuales en un momento se almacenará la línea actual y en la otra se almacenará la línea anterior. De esta manera el tiempo de acceso - requerido ahora sefa de 70 ns para lectura y 70 ns para escritura como máximo.

En el anexo 4 se muestra el plano del cir cuito final de esta etapa en el que como se aprecia se ha realizado un arreglo de memoria para llegar a la capacidad requerida de 910 bytes. En el anexo 9 se podrá verificar las especificaciones técnicas de la memoria utilizada.

El control de la memoria se realiza bascu lando cada 910 muestras la línea de  $R/\bar{w}$ ; esto se rea liza con un contador 910 y un FLIP-FLOP tal como se aprecia. Además se hace un pequeño retardo del reloj principal para controlar los latches que recogen los datos de la memoria con el fin de capturarlos en es tabilidad.

#### CAPITULO VI

#### IMPLEMENTACION DEL SISTEMA PROPUESTO

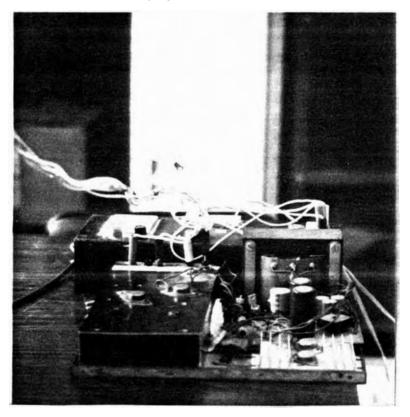

# 6.1 Introducción

El sistema propuesto fue desarrollado en el laboratorio de Investigación del Instituto Nacio nal de Investigación y Capacitación en Telecomunica ciones (INICTEL) quedando así como el primer prototipo en su especie desarrollado en el país.

En este capítulo se dará a conocer los de talles más importantes del proceso de implementación así como también algunos problemas presentados y las soluciones adoptadas.

# 6.2 Tarjetas Impresas

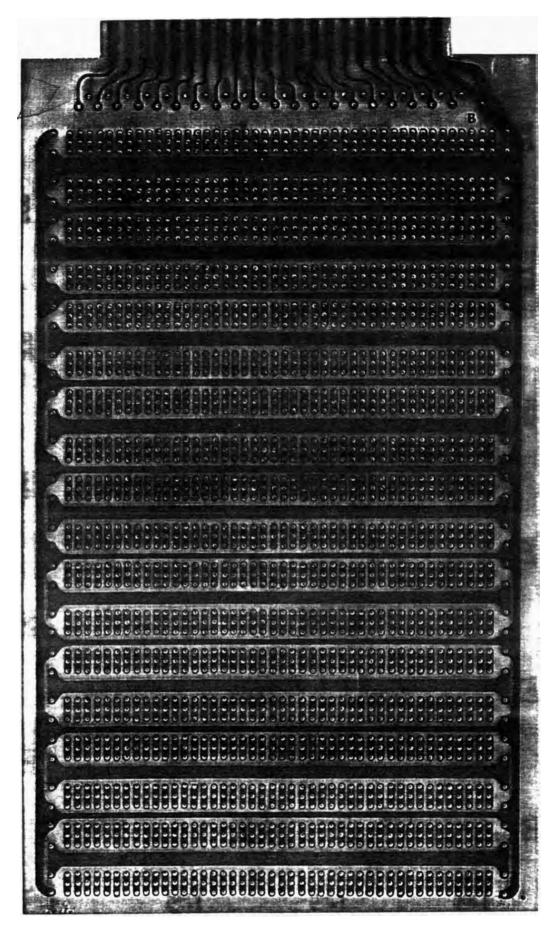

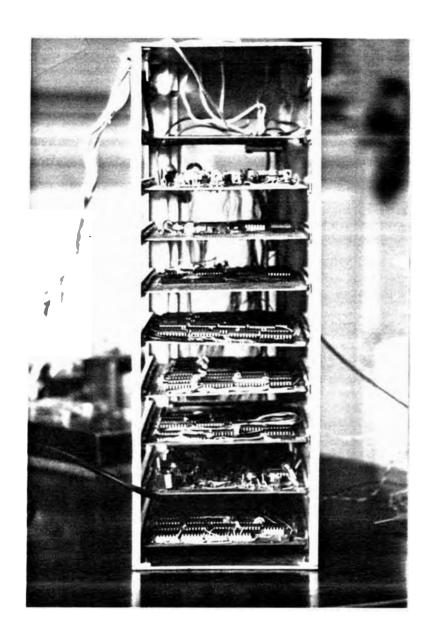

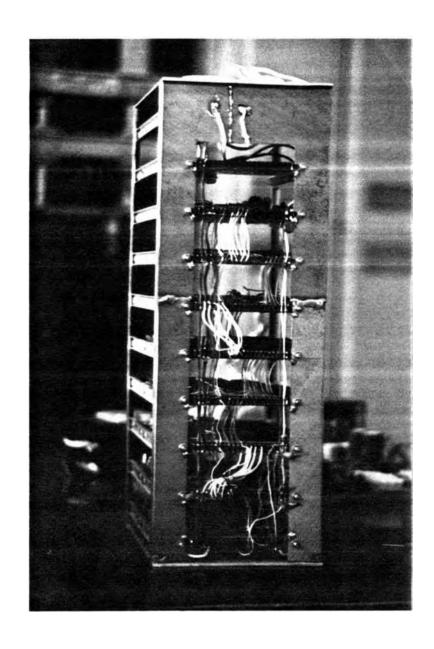

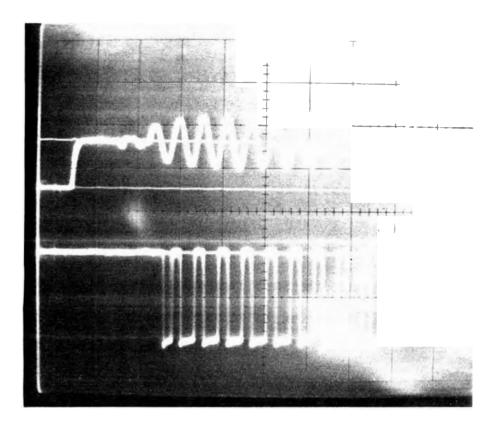

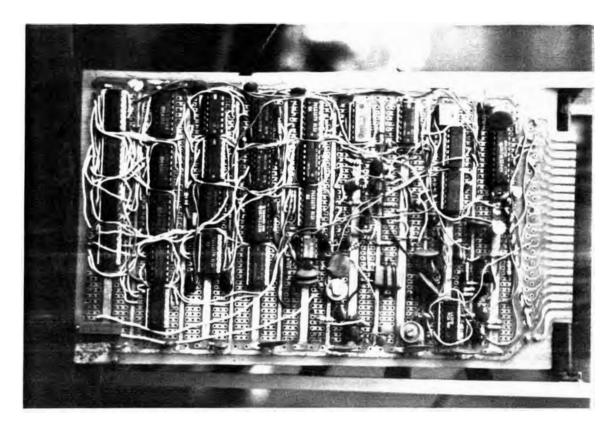

Las distintas etapas del sistema fueron implementadas en tarjetas de circuito impreso especialmente diseñadas para propósitos experimentales.